TSMCの14nm世代への移行は遅れる可能性も、「原因は経済的な問題」:ビジネスニュース

TSMCの14nmプロセスへの移行が、スケジュール通りにはいかない可能性が出てきた。同社のShang-Yi Chiang氏は、この原因を「技術的な問題というより、経済的な問題である」とし、「リソグラフィ技術の選択について決断を急ぐ必要がある」と語った。

「14nmプロセス技術への移行に関して、製造装置メーカーの対応が遅れている。14nmプロセスのチップの製造を2015年に開始するためには、重要な決断を下すべき時に来ている」。TSMC(Taiwan Semiconductor Manufacturing Company)で研究開発担当シニアバイスプレジデントを務めるShang-Yi Chiang氏は、2011年9月7〜9日に台湾の台北で開催された半導体関連の国際展示会「Semicon Taiwan 2011」でこのように語った(図1)。

TSMCは、14nmプロセスのチップの製造を効率よく進めるには、適切なリソグラフィ技術の選択と450mmウェハーへの移行が不可欠だとしている。しかし、装置メーカーの対応が遅れており、TSMCのスケジュール通りにはいかない可能性も出てきているという。Chiang氏は、「14nmプロセスへの移行に間に合わないのではないかという不安が、日に日に募ってくる」と明かした。

半導体ファブでは、1時間当たりウェハー100枚以上というスループットが必要となる。しかし、EUV(Extreme Ultraviolet:極端紫外線)リソグラフィ技術では、まだそこまでのスループットを実現できていない。また、マルチプル電子ビームリソグラフィ技術では、スループットはさらに低くなる。

TSMCは数カ月前に、450mmウェハーへの移行に必要となる設備一覧を公開した。しかし、Chiang氏がEE Timesに語ったところによると、「製造装置メーカーの間では、450mmウェハーへの移行はまだ時期尚早だとの見方が強く、先行きは不透明だ。200mmと300mmウェハーで130nm世代を導入した際もかなり苦労を強いられたが、今回も同様の状況になってしまうかもしれない」という。

「技術的な問題ではなく、経済的な問題」

TSMCは、台湾の台中に建設を予定している450mmファブ「Fab 15」に続き、新竹にある「Fab 12」でも450mmウェハーのパイロット製造ラインを立ち上げる計画だという。ウェハー面積を大きくすれば、ムーアの法則を実現できると同時に、ウェハーの製造コストを約30%削減することも可能になるとしている。

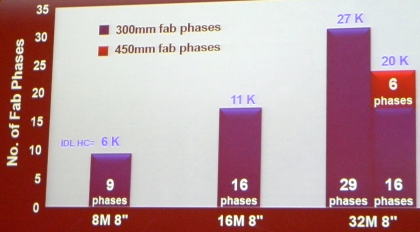

450nmウェハーへ移行すれば、半導体製造に必要なファブの数を減らすことができるため、施設と技術者にかかるコストを大幅に削減できる。ウェハーの需要は3200万枚(8インチ換算)に上るとみられており、TSMCがこれに対応するには、22のファブと2万人の技術者が必要になる。しかし、現行の300mmウェハーで対応する場合は、29のファブと2万7000人の技術者が必要になるという(図2)。

Chiang氏は、「450mmウェハーの導入を阻んでいるのは、技術的な問題ではなく経済的な問題だ。現在の状況では、技術的な問題よりも経済的な問題がより重要になっている」と語る。

リソグラフィ技術については、波長が193nmの液浸リソグラフィ技術を、TSMCが現在適用している28nmプロセスと次世代の20nmプロセスの両方に対応させる考えだ。ただし、20nm世代では、より微細な回路を作り込むために、露光プロセスを2回繰り返すダブルパターンニングが必要になるという。

14nmプロセスのチップの製造に、ダブルパターニングを導入した液浸リソグラフィを用いるとなると、製造コストが飛躍的に高くなってしまう。TSMCはこの課題に対処するために、今後数週間以内に、ASMLのEUVリソグラフィ装置「3100シリーズ」のプロトタイプを試験的に導入する予定だとしている。

Chiang氏は、「2012年の早い時期に、リソグラフィ技術の選択について決断を下さなければならない。いったん193nm液浸リソグラフィを適用すると決めたら、後からEUVリソグラフィに転向するのは非常に難しくなる。デザインルールはリソグラフィによって決まるので、迷っている時間はない」と語った。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

図1 TSMCのShang-Yi Chiang氏

図1 TSMCのShang-Yi Chiang氏 図2 450mmウェハー導入のメリット 450mmウェハーを使用すれば、ファブの数も技術者の人数も低減することができる。

図2 450mmウェハー導入のメリット 450mmウェハーを使用すれば、ファブの数も技術者の人数も低減することができる。