アルテラも28Gbps波形を披露、ロジック部も動作させ実際の利用形態に近く:ET2011 高速シリアルインタフェース技術

ET2011でFPGA大手ベンダーの日本アルテラは、最先端FPGAの高速シリアルトランシーバ(SERDES)の動作を披露した。従来公表していたのは、SERDESチップ単体での伝送波形だった。今回はFPGAのロジック部とともにSERDES回路を1枚のチップに集積したエンジニアリングサンプル品を使っている。

日本アルテラは、2011年11月16〜18日に開催された「Embedded Technology 2011/組込み総合技術展(ET2011)」(会場はパシフィコ横浜)で、28nm世代の半導体製造技術を適用する次期FPGAのハイエンド品「Stratix V」のうち、28Gビット/秒対応の高速シリアルトランシーバ(SERDES:シリアライザ/デシリアライザ)を4チャネル搭載する「Stratix V GT」のエンジニアリングサンプル品を実際に動作させ、そのデータ伝送波形を披露した。

同社はこれまでも28Gビット/秒の伝送波形を公表していたが、それはSERDESチップ単体での波形だった。それに対し今回のデモでは、FPGAのロジック部とSERDES回路を1枚のチップに集積し、それをパッケージに集積した、最終的な製品の形態での動作を実演した。FPGAのロジック部にも、小規模ながら評価用のロジックを実装して同時に動作させている。「ロジックがノイズ源になるので、SERDES単体ではなく、この方が実際の使用状態により近い波形で評価できる。しかも、SERDESの特性設定ツールのチューニングでさらに波形品質を高められることを確認済みだ。当社は、10Gビット/秒を超える高速シリアルトランシーバ技術では、競合他社の1歩、2歩先をいっている」(同社の説明員)。

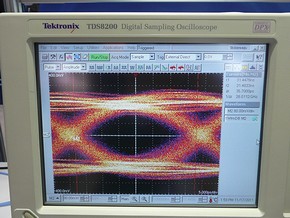

左側の写真は、デモの全景である。Stratix V GTのエンジニアリングサンプル品を評価ボードに実装し、内蔵の高速SERDESを28Gビット/秒で動作させ、データ伝送波形をサンプリングオシロスコープで観測して見せていた。PRBS 7の疑似ランダムパターンを伝送しているところだ。右側の写真は、サンプリングオシロスコープの画面である。ジッター測定のオプション機能を搭載していない機体を使ったため、ジッターの測定値は画面からは読み取れない。(クリックで拡大)

左側の写真は、デモの全景である。Stratix V GTのエンジニアリングサンプル品を評価ボードに実装し、内蔵の高速SERDESを28Gビット/秒で動作させ、データ伝送波形をサンプリングオシロスコープで観測して見せていた。PRBS 7の疑似ランダムパターンを伝送しているところだ。右側の写真は、サンプリングオシロスコープの画面である。ジッター測定のオプション機能を搭載していない機体を使ったため、ジッターの測定値は画面からは読み取れない。(クリックで拡大)このStratix V GTの28Gビット/秒SERDESは、OIF(Optical Internetworking Forum)が定める電気インタフェースの共通仕様「CEI-28G」で、20cm程度の伝送可能距離を求める「SR(Short Reach)」を満たすという。消費電力については、現時点では「28Gビット/秒動作時にチャネル当たり200mW以下を目標にしている」(同社の説明員)とした。

同社は2012年の早い時期に、このStratix V GTの評価ボードの出荷を始める予定だという。なお、最大14.1Gビット/秒のSERDESを搭載する「Stratix V GX」については、すでにエンジニアリングサンプル品を実装した評価ボードの受注を開始しており、一部の顧客には納入済みだとしている。ただしこのエンジニアリングサンプル品は、現在のところSERDESの動作速度が最大12.5Gビット/秒にとどまっている。

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待