消費電力1/100に! 夢の“不揮発ロジック”の実用化へ前進:プロセス技術 不揮発ロジック(1/3 ページ)

NECと東北大学は、スピントロニクス技術のロジックLSI分野への応用の道を開く2つの開発成果を発表した。2者は、「今回の開発成果をさらに進化させ、2017年頃には商用デバイスに技術を反映させたい」とする。

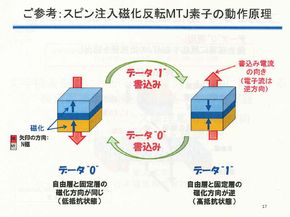

スピントロニクスとは、電子のスピン(磁石の性質)とマイナス電荷の両方を利用する技術のことを指す。このスピントロニクスを応用したデバイスの開発が盛んになっている。マイナス電荷の流れでN極/S極の向きを変える微細な磁石である「スピン注入磁化反転型磁気トンネル接続(MTJ)素子」と、電荷を制御する従来の半導体デバイス技術「CMOS技術」を組み合わせたデバイスの開発が進められている。

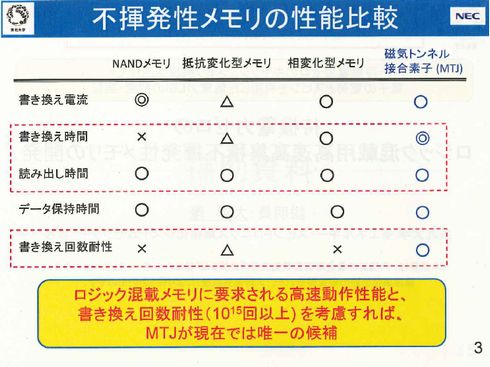

MTJ素子は、電源を遮断してもデータを失わない不揮発性メモリの記憶素子として利用可能だ。加えて、他の不揮発性メモリに比べても多くの利点を持つ。書き込み/読み出し時間が短く、書き換え耐性も高い。そのため、MTJ素子を使ったメモリ「MRAM」は、DRAMに取って代わる次世代メモリとして、Samsungや東芝、SK Hynixなど大手メモリメーカーがこぞって積極的な開発を進める他、MRAMを専業とするベンチャー企業なども登場している(関連記事:スピン注入式の新型MRAMがいよいよ製品化、2015年にはギガビット品が登場へ)。

DRAMなどあらゆる単体メモリに代わるユニバーサルメモリとして注目を集め、実用化が迫るスピントロニクス、MTJ素子だが、NECと東北大学は、ロジックLSIにMTJ素子を適用することで、超低消費電力、待機電力ゼロのロジックLSIを実現すべく、研究開発を進めている。

NECと東北大学によるスピントロニクス応用デバイスを作製した300mmウエハー。国内半導体メーカーの300mmウエハー対応ラインで90nmプロセスでトランジスタ、配線層を構成した後、「つくばイノベーションアリーナ」(TIA)でMTJ素子を作製したという (クリックで拡大)

NECと東北大学によるスピントロニクス応用デバイスを作製した300mmウエハー。国内半導体メーカーの300mmウエハー対応ラインで90nmプロセスでトランジスタ、配線層を構成した後、「つくばイノベーションアリーナ」(TIA)でMTJ素子を作製したという (クリックで拡大)ロジックLSIは、製造プロセスの微細化に伴い消費電力量が増大している。回路規模の増大に伴う電力消費量の増加やリーク電流の増大といったことが原因だ。NECと東北大は、この増大するロジックLSIの電力消費量を減らすため、ロジック回路と混載するキャッシュメモリ領域の記憶素子をMTJ素子で構成し、従来のSRAMなどで必要だったデータ保持用の電力を削減しようとしている。同時に、ロジックLSIの回路構成自体を見直し、演算素子毎に不揮発記憶素子を持たせ電源が完全に遮断されても回路状態を保持する「ロジック・イン・メモリ」構造で、待機電力ゼロのロジックLSIを実現しようという開発も進めている。

今回、2者が発表を行った成果は2件で、混載メモリ、ロジック・イン・メモリそれぞれでMTJ素子の実用化に近づく開発成果となった。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- 「3社のパワー半導体事業を切り出し合弁設立したい」三菱電機社長