消費電力1/100に! 夢の“不揮発ロジック”の実用化へ前進:プロセス技術 不揮発ロジック(2/3 ページ)

L3キャッシュ程度の混載メモリでのMTJ素子応用にメド

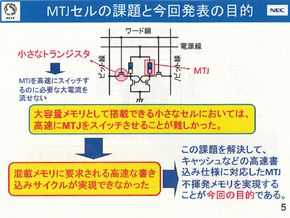

プロセッサなどのデバイスに混載されるキャッシュメモリは、マルチコア化などに伴い容量が増大する傾向にあり、キャッシュメモリ部の待機電力も大きくなっている。そのため、キャッシュメモリを不揮発化しようとしている。ただ、キャッシュメモリは、DRAMなどのメインメモリに比べ、容量は小さいものの高速なアクセススピードが求められる。キャッシュメモリに、MTJ素子による不揮発性メモリを用いるには、現行のSRAMと同様のアクセススピードを実現する必要がある。

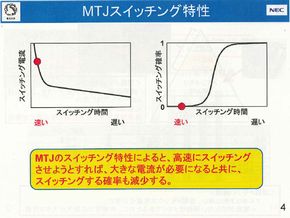

しかし、MTJ素子を高速にスイッチング動作させるには、大きな電流が必要となる。大電流を流すためには、トランジスタ構造が大きくなるとともに、消費電力が増大する。さらに、スイッチング時間が短くなるとスイッチング確率(正しくスイッチングする確率)も著しく低くなるという課題を持つ。これまで、NECと東北大が開発してきた混載メモリでも書き込み時間は40ns程度と、2ns程度のSRAMに比べ遅く、混載メモリとして応用するためのネックとなっていた。

MTJ素子への書き込み要する時間だけSRAMでデータ保持

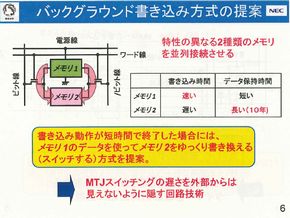

今回、2者は、L3キャッシュメモリで要求される2ns程度の高速書き込みを実現するため、SRAMとMTJ素子を組み合わせた「バックグラウンド書き込み方式」を考案した。この方式は、書き込みが高速なSRAMとMTJ素子を併用するもので、とりあえずSRAM側は2nsという短時間で書き込みを終える。同時に、同じデータをMTJ素子側は、5ns程度の時間をかけてゆっくりと書き込むという仕組みだ。回路の工夫で、CPUなどキャッシュメモリを使う側には、MTJ素子の書き込みの遅さは見えず、従来のSRAM同様のアクセススピードで使用できる。また、2者は、MTJ素子の書き込みが終了した後に、電源を遮断するタイマーを電源分割単位毎に構成する技術も合わせて開発。そのため、SRAMのデータ保持は、MTJ素子への書き込みが完了するまでの暫定的なものであり、大部分の時間はMTJ素子のみでデータを保持するため、SRAMでの電力消費はわずかだ。

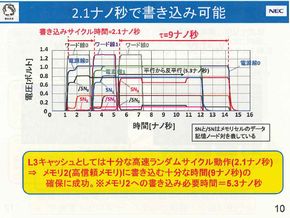

左は、「バックグラウンド書き込み方式」のイメージ。右は、SRAM、MTJ素子の書き込み時間のグラフ。SRAMは2.1nsの書き込み動作で動く一方、黒い線で表しているMTJの書き込みは5.3nsを費やしている。タイマーにより、9nsでメモリセルへの電源を落としている (クリックで拡大) 出典:NEC/東北大学

左は、「バックグラウンド書き込み方式」のイメージ。右は、SRAM、MTJ素子の書き込み時間のグラフ。SRAMは2.1nsの書き込み動作で動く一方、黒い線で表しているMTJの書き込みは5.3nsを費やしている。タイマーにより、9nsでメモリセルへの電源を落としている (クリックで拡大) 出典:NEC/東北大学SRAMとMTJ素子を双方を使用するため、チップサイズの増大が懸念されるが、MTJ素子はトランジスタ上に構成できるため、一般的な6トランジスタ構成のSRAMとチップサイズは変わらないという。

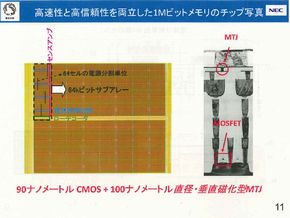

今回、90ナノCMOSプロセスを使用しバックグラウンド書き込み方式を使った1Mビット容量の混載メモリを試作した結果、電源電圧1.3Vでの動作、2.1nsという高速書き込みが行えることを確認し、「L3キャッシュレベルでMTJ素子が応用できる基盤技術が確立できた」(NEC/東北大学)としている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待