ARMから見た7nm CMOS時代のCPU設計(6)〜レイアウトの実際:福田昭のデバイス通信(17)(1/2 ページ)

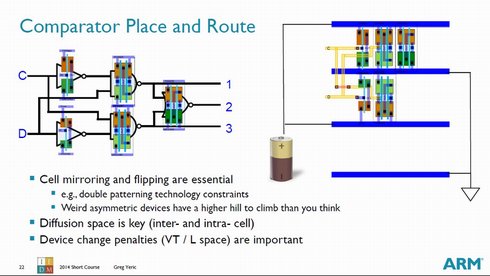

今回は、回路がどのようにレイアウトされていくのかを見てみよう。回路図が同じでも、実際にシリコンのスタンダードセルとして具現化すると、レイアウトがだいぶ異なる場合もある。ARMの講演では、コンパレータを例に取って説明していた。

コンパレータ(比較器)のレイアウト

前回は、スタンダードセルの概要を説明した。それでは、実際の回路がどのようにレイアウトされていくのかを見てみよう。ARMの講演では、コンパレータ(比較器)の例を挙げていた。

入力信号Cと入力信号Dの値を比較するコンパレータは、2個のインバータと2個の2入力NAND、1個のNORで構成される。レイアウトは対称形が基本である。初段の2個のインバータは、接地配線を中央に、その上下に1個ずつ、対称に配置する。次段の2個のNANDゲートも同様に、接地配線を中央にして対称にレイアウトする。最終段のNORゲートは上部に配置する。

ここで重要なのは、各CMOSゲートにおける拡散層(ソースあるいはドレインになる層)の大きさである。拡散層の大きさが、トランジスタの電流駆動能力を決めるからだ。負荷容量の大小を考慮し、さらにnMOSトランジスタとpMOSトランジスタの違いに配慮して、拡散層の寸法を決める。

負荷容量が大きいときに、遅延時間を短縮するためには拡散層を大きめに確保してゲート幅を広くとらなければならない。また通常のトランジスタは、同じ寸法だとnMOSトランジスタの電流駆動能力がpMOSトランジスタよりも高い。そこで普通は拡散層のサイズを調節して、nMOSとpMOSの電流駆動能力を同じにする必要がある。

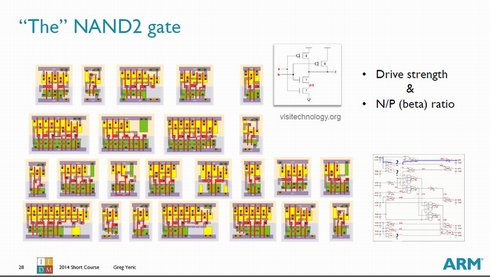

同じ種類のゲートでもセルレイアウトは多種多様

したがって同じ種類のゲートでも多種多様なセルレイアウトが存在することになる。講演では、2入力NANDゲートのスタンダードセルを例示し、24種類ものレイアウトを見せていた。

回路図では、2入力NANDゲートは2個のpMOSトランジスタと2個のnMOSトランジスタの組み合わせで表記される。24種類のセルレイアウトは、回路図では全て同じだ。しかしシリコンのスタンダードセルとして具現化すると、数十種類の異なる「レイアウト」が姿を現す。実際のシリコン集積回路の姿に比べると、回路図がいかに抽象的なものであるかが、よく分かる。

言い換えると、回路図だけでは、シリコンの集積回路を具体的には決められない。シリコンの集積回路を決めるのは、マスクパターンの集合だ。回路図をマスクパターンの集合に変換するのが、本シリーズの第3回で説明した設計工程(配置工程や配線工程など)なのである。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」