ARMから見た7nm CMOS時代のCPU設計(6)〜レイアウトの実際:福田昭のデバイス通信(17)(2/2 ページ)

スタンダードセルの数は1300〜1500個

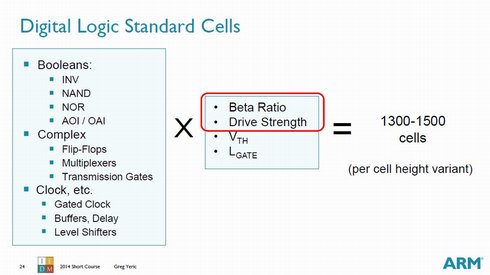

回路図とマスクパターンの間に存在するパラメータは、大きく分けると4つある。1つは、(1)pMOSトランジスタのベータ値とnMOSトランジスタのベータ値の比率(ベータ比[Beta Ratio])である。もう1つは、(2)トランジスタの電流駆動能力(ドライブ強度[Drive Strength])だ。3番目は、(3)トランジスタのしきい電圧(VTH)である。最後は、(4)ゲート長(LGATE)だ。

(1)でベータ比が1のときは電源電圧の半分の入力電圧が、スイッチング電圧になる。ベータ比が1を超えていく、つまり、pMOSのベータが相対的に大きくなるときは、スイッチング電圧は上昇する。反対にベータ比が1から下がっていく、つまり、nMOSのベータが相対的に大きくなるときは、スイッチング電圧は下降する。

(2)で電流駆動能力を上げるための基本的な方法は、ゲート幅を広げることである。ただしゲート幅を広げると、ゲートの静電容量が増加し、前段のトランジスタから見た負荷容量が増える。

(3)で電源電圧が同一の場合、しきい電圧と電源電圧の差によって電流駆動能力が決まる。つまり、しきい電圧が低いと電流が増加する。ただし、しきい電圧を下げるとリーク電流が増加し、待機時消費電力の増大を招く。

(4)でゲート長を短くすると、トランジスタのゲート幅当たりの電流駆動能力が増加する。ただしゲート長を短くするとセルレイアウト全体の単位寸法(ゲートピッチ)が短くなるとともに、製造が難しくなる。

論理ゲートやフリップフロップ、バッファなどのスタンダードセルは、これら4つのパラメータの違いにより、レイアウトの異なる数多くの派生品を生み出す。1個のセルライブラリ(同じ高さのセル群によるライブラリ)は、おおよそ1300個〜1500個と数多くのセルで構成されているという。

(次回に続く)

関連記事

ARMとSpansionが車載エレクトロニクスと車載マイコンを解説

ARMとSpansionが車載エレクトロニクスと車載マイコンを解説

ARMとSpansionは2015年3月26日、横浜市で報道機関向けの説明会を開催し、自動車用エレクトロニクスと車載用マイコンの動向を解説した。 「コンパレータ」の選択基準

「コンパレータ」の選択基準

コンパレータは、2つの電圧を比較して、どちらが高いかを判断するという、単純で基本的な処理を行う部品である。その一方で、理解しておくべき仕様が無数に存在するため、コンパレータを用いた回路の設計は容易だとは言えない。本稿では、まずオペアンプとの比較を通し、コンパレータの特徴について説明する。その上で、コンパレータを選択する際に検討すべき6つのポイントについて解説する。 トランジスタも捨てたものではない

トランジスタも捨てたものではない

さまざまな機能の回路がIC化されて流通している現在、個別素子のトランジスタを使う機会は少ないという方もいるかもしれない。しかしトランジスタは応用範囲が広く、使いこなせばとても便利だ。今回は、通常はオペアンプICやコンパレータICを使って構成する回路を、わずか3個のトランジスタで作る方法を紹介しよう。 ARMが新プロセッサ「Cortex-M7」を発表、「コネクテッドカーを進化させる」

ARMが新プロセッサ「Cortex-M7」を発表、「コネクテッドカーを進化させる」

ARMは、マイコン向け32ビットプロセッサコア「Cortex-Mシリーズ」の新製品となる「Cortex-M7」を発表した。従来品の「Cortex-M4」と比べて、演算処理性能およびデジタル信号処理(DSP)性能を大幅に高めた。 ARMが語る、IoTセキュリティの将来像

ARMが語る、IoTセキュリティの将来像

モノのインターネット(IoT)において、セキュリティへの懸念は増すばかりである。このような背景の下、ARMが、IoT向けセキュリティソフトウェアを手掛けるオランダのOffsparkを買収したと発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」