デバイス技術の注目論文 〜7nm以降を狙う高移動度トランジスタ:VLSIシンポジウム 2015 プレビュー(2)(1/4 ページ)

今回は、メモリ分野、先端CMOS分野、非シリコン分野における採択論文の概要を紹介する。抵抗変化メモリ(ReRAM)や3次元縦型構造の相変化メモリ(PCM)に関する論文の他、GaNやSiGe、InGaAsなど、次世代の高移動度の化合物半導体を用いたトランジスタに関する技術論文の概要が紹介された。

メモリ分野と先端CMOS分野がデバイス技術をけん引

VLSIシンポジウム委員会は4月20日に東京で報道機関向けの説明会を開催し、今年6月に開催されるシンポジウムの概要を説明した。前回に続き、説明会の内容をお届けする。

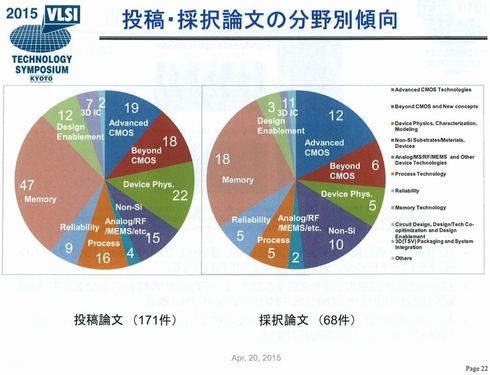

説明会では、総合委員長の黒田氏の後に、VLSI Technologyのシンポジウム委員長を務める平本氏がVLSI Technologyの概要を説明した。続いてプログラム委員長を務める稲葉聡(いなば・さとし)氏(東芝エレクトロニクス韓国社)が登壇し、始めに投稿論文と採択論文の分野別割合を説明した。

投稿論文の数が最も多いのはメモリ分野で、47件を数える。次いでデバイス物理分野が22件、先端CMOS分野が19件、CMOSを超えるデバイスの分野が18件と続く。

採択論文の数が最も多いのは投稿論文と同様、メモリ分野である。18件の論文が採択された。次いで先端CMOS分野が12件、非シリコン分野が10件と続く。非シリコン分野の投稿数は15件とそれほど多くはない。採択率が3分の2と高いことが、採択論文の多さにつながっている。一方で投稿論文数で第2位に付けたデバイス物理分野の採択論文数は、5件にとどまる。

Intelが14nmのSoC向けプラットフォーム技術を発表

続いて稲葉氏は、シンポジウム委員会が選んだ注目すべき発表(注目論文)を紹介した。量産が始まりつつある最先端デバイス技術の論文や、将来のデバイスを支える要素技術の論文など、多種多様な11件の発表が選ばれた。

11件の論文を詳しく紹介してしまうと、肝心の発表に関する興味が削がれてしまいかねない。そこで説明会では、11件のそれぞれについて要点だけを開示することにとどめていた。

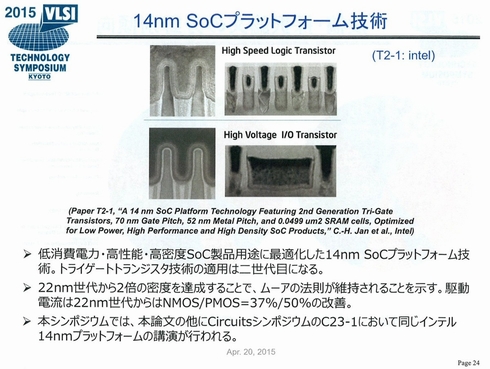

最初に紹介したのは、14nmのSoC向けCMOSプラットフォーム技術に関する発表である。発表者はIntel。前世代の22nm世代で導入したトライゲート(FinFET)技術を14nmでも採用している。「第2世代のトライゲート技術」とIntelは呼称する。

次に、7nm世代以降のCMOSロジック向け金属配線技術に関する発表を紹介した。発表者はIBMとGLOBALFOUNDRIES。28nmピッチと極めて細い銅配線を、誘導自己組織化(DSA)技術によるパターニングと銅リフローによって形成した。竹の節のような粒子構造(「バンブー・グレイン」)を制御することで、7nm世代の銅配線の抵抗率上昇を抑制する可能性が出てきたとする。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増