EE Times Japan >

プロセス技術 >

デバイス技術の注目論文 〜7nm以降を狙う高移動度トランジスタ:VLSIシンポジウム 2015 プレビュー(2)(4/4 ページ)

» 2015年04月28日 08時00分 公開

[福田昭,EE Times Japan]

7nm世代のモバイルSoC向け全体最適化技術

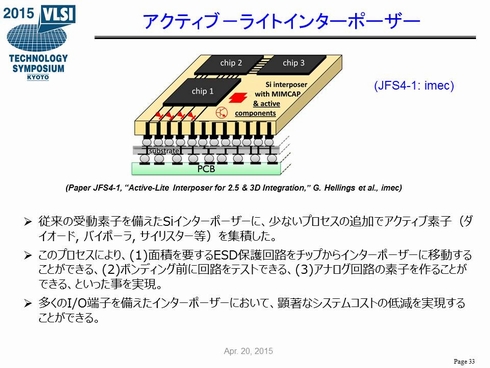

それから、シリコンのインターポーザにアクティブ素子を形成する技術の開発成果を紹介した。発表者はimec。2.5次元あるいは3次元のシリコンダイ積層モジュール向けである。マスク数の少ないプロセスで、シリコンのインターポーザにダイオードやバイポーラ・トランジスタなどのアクティブ素子を形成する。ESD保護回路やテスト端子回路、アナログ回路を形成することで、シリコンダイ側のコストを削減する。

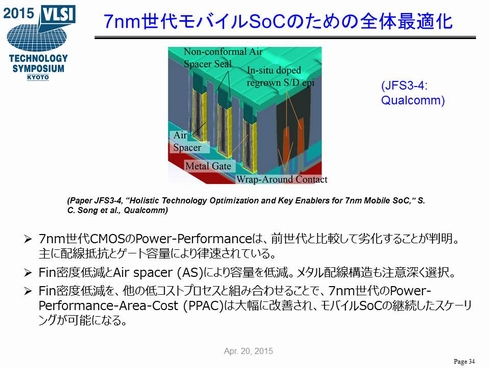

最後に紹介したのは、7nm世代のモバイルSoC向け全体最適化技術である。発表者はQualcomm。7nm世代では、配線抵抗とゲート容量の増加によってCMOSデバイスの速度対消費電力の性能が向上しなくなる。そこでFinFETのフィン密度を低減する、FinFETの側壁絶縁膜をエアギャップに変更するといった工夫で容量の増加を抑える。配線に関しては配線経路や階層構造などを注意深く調整し、配線抵抗の増加を避ける。こういった工夫などによって7nm世代のモバイルSoCでもスケーリングを可能にする。

(次回に続く)

関連記事

14nm SoCや新規メモリなどの研究成果を発表へ――日本の採択論文数は米国に次ぐ計27件

14nm SoCや新規メモリなどの研究成果を発表へ――日本の採択論文数は米国に次ぐ計27件

2015年6月に開催される国際学会「VLSI Technologyシンポジウム」と「VLSI Circuitsシンポジウム」の概要が明らかになった。IoT(モノのインターネット)社会の実現に向けたLSIのデバイス技術と回路技術などに関して、最先端の研究成果が披露される予定である。 ムーアの法則、50年をたどる

ムーアの法則、50年をたどる

1965年、IntelのGordon Moore(ゴードン・ムーア)氏が雑誌に掲載したトランジスタに関する予見は、「ムーアの法則」として半導体技術の発展の大きな原動力となった。ムーアの法則によってトランジスタがどれほど進化してきたのか。50年を振り返ってみる。 TSMC、10nmプロセスではインテルとの技術差なくなる

TSMC、10nmプロセスではインテルとの技術差なくなる

TSMCは、10nmプロセスを適用したチップの製造を2017年に開始する。同社は「インテルの10nmチップと同等レベルの性能を実現できると見ている。10nmプロセスで、インテルとの技術的なギャップを埋められるだろう」と述べている。 TSMC、2015年半ばに16nm FinFETの量産開始へ

TSMC、2015年半ばに16nm FinFETの量産開始へ

TSMCは、16nmプロセス以降のロードマップを明らかにした。まずは2015年半ばに、16nm FinFET+を適用したチップの量産を開始する。2016年には、10nmチップの生産工場の建設にも着手する。 Samsungが14nm世代のFinFETを展示、仕様は明かさず

Samsungが14nm世代のFinFETを展示、仕様は明かさず

Samsung Electronics(サムスン電子)が、ARM主催のイベントで14nm世代のFinFETプロセス技術を適用したチップを発表した。TSMCもその直前に16nm FinFETプロセスを用いたARM「Cortex-A57」の検証を行っているが、ある専門家は、16/14nm FinFETの性能については、SamsungとTSMCは互角だとみている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 次世代パワー半導体 「期待の5材料」の現在地

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」

Special SitePR

あなたにおすすめの記事PR