EE Times Japan >

プロセス技術 >

デバイス技術の注目論文 〜7nm以降を狙う高移動度トランジスタ:VLSIシンポジウム 2015 プレビュー(2)(3/4 ページ)

» 2015年04月28日 08時00分 公開

[福田昭,EE Times Japan]

次世代の高移動度材料によるトランジスタ要素技術

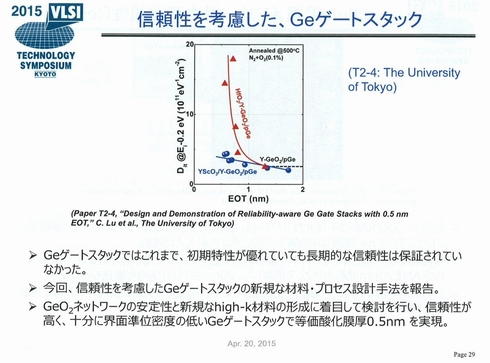

それから、次世代の高移動度トランジスタ材料として期待されているゲルマニウム(Ge)半導体トランジスタに関する要素技術の発表を紹介した。発表者は東京大学である。長期的な信頼性を考慮したGeゲートスタックの絶縁材料として二酸化ゲルマニウム(GeO2)を採用し、酸化膜換算で0.5nmと薄いゲート絶縁膜と、長期信頼性を両立させた。

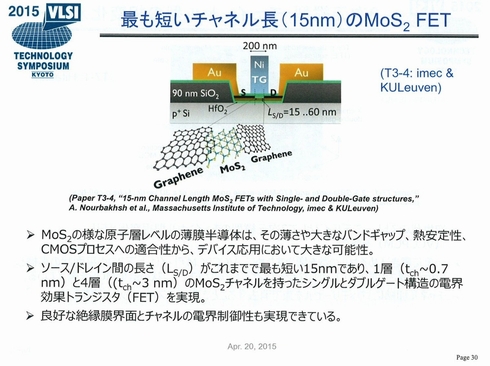

次に同じく次世代の高移動度材料として期待されている二硫化モリブデン(MoS2)をチャンネル材料とするトランジスタ技術の研究成果を、取り上げた。発表者はimecとKU Leuvenである。原子層レベルの薄いグラフェン材料をソースとドレインに用い、単原子層(コンタクト用)と4原子層の極めて薄いMoS2層をチャンネルとしたFETを試作している。ソースとドレインの間隔は15nmと短い。

高い信頼性を確保した混載用不揮発性メモリ

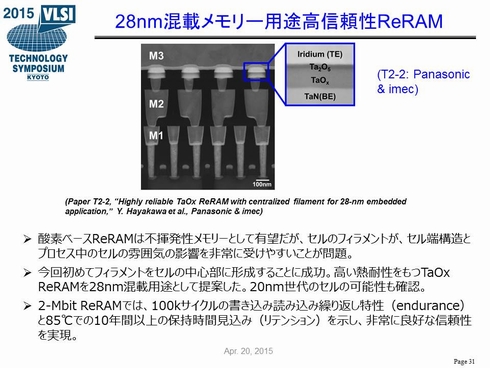

ここからは、不揮発性メモリ技術に関する注目論文を2件、紹介する。1件は、ロジックとの混載を目的とした抵抗変化メモリ(ReRAM)技術である。発表者はimecとパナソニック。28nm技術による高信頼の2MビットReRAMマクロを試作し、85℃で10年間のデータ保持寿命と10万回の書き換えサイクル寿命を確認した。

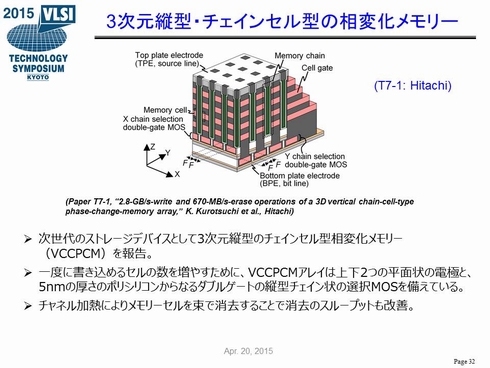

もう1件は、3次元縦型構造の相変化メモリ(PCM)技術である。発表者は日立製作所。縦型の多結晶シリコンMOSメモリセルが連なるチェインセル構造を採用して記憶密度を高めた。書き換えのスループットを向上するため、複数のメモリセルのデータをまとめて消去可能な構造としている。消去動作のスループットは670Mバイト/秒、書き込み動作のスループットは2.8Gバイト/秒に達する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 次世代パワー半導体 「期待の5材料」の現在地

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」

Special SitePR

あなたにおすすめの記事PR