SRAM同様、自由に配置できる混載フラッシュ:マスク4枚を追加するだけの低コスト製造対応(2/4 ページ)

高圧MOSが必要

フラッシュメモリが高圧を必要とする理由は、絶縁膜に挟まれた記憶領域(フローティングゲート方式では浮遊ゲートに相当)にホットエレクトロン効果ないしFN(Fowler-Nordheim)トンネル効果を利用して、電荷を出し入れするためには高い電圧が必要なためだ。1〜3V程度で駆動する通常のCMOSに対し、10Vを上回るような高圧MOSが必要になる。

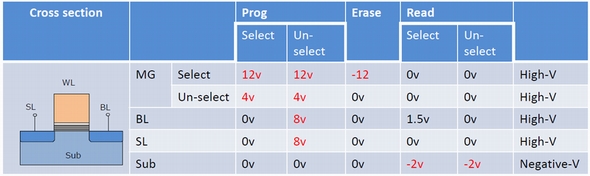

高圧MOSが必要となる一例として、チャージトラップ方式でFNトンネル効果を利用するSONOS構造のフラッシュメモリを見てみよう。下図の左側に示した図が、同メモリセルの断面図だ。

電荷を保持するSiN膜(シリコン窒化膜)の記憶領域(グレーの部分)に電荷を注入するためには、メモリゲートに10V前後の高圧(ここでは12V)を掛ける必要がある。電荷を取り除く(消去する)場合は逆に、マイナスの高圧(ここでは−12V)を掛ける必要が生じる。

読み出しに関しては、ソースに電圧を掛け、ドレイン側の電流値で記憶領域内の電荷の有無を検出する。この時にソースに与える電圧は、ロジックなどのスタンダードCMOSの低い駆動電圧(コア電圧)で十分だ。

問題となるのは「非セレクト」

これだけであれば、ソース、ドレインに高圧を掛ける必要はないのだが、ソース、ドレインにも、高圧を掛ける必要がある。それは、書き込み時に、電荷を注入しない「非セレクト」(Un-select)の場合だ。電荷を注入する「セレクト」(select)、「非セレクト」にかかわらず、構造上、メモリゲートに電荷注入用の高圧が掛かる。非セレクトのメモリセルでFNトンネル現象を起こさないために、メモリゲートと記憶領域間に電位差が生じないよう、ソース、ドレインにも一定の高圧(ここでは8V程度)を印加しなければならない。そのためメモリセル全体として、高圧MOSで構成しなければならないのだ。

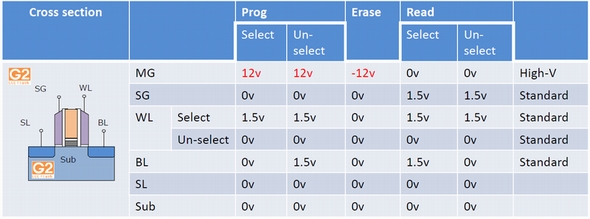

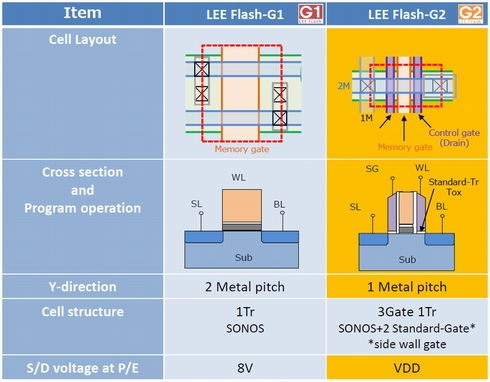

これに対し、フローディアが開発したLEE Flash-G2は、メモリゲートに対し高圧を掛ける必要があるが、ソース/ドレインについては、高圧を掛ける必要がなくコア電圧で済むようにした技術だ。

LEE Flash-G2のメモリセルの断面図が下図だ。メモリゲートの両サイドにもゲートを追加した構造だ。この追加したゲートは「セレクトゲート」と呼び、電荷の注入、すなわちFNトンネル注入を起こす起こさないを制御するゲートになる。

メモリゲート自体には、12Vの高圧を掛けるが、セレクトゲートには高圧を掛ける必要がない。1.5V程度のコア電圧だけで、FNトンネル注入を起こすチャネルの電流を制御できるためだ。「小さな力で、大きな力を操るIGBT(絶縁ゲート型バイポーラトランジスタ)のフラッシュメモリ版のような仕組み」(同社アドバイザーを務める柳沢一正氏)だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増