次々世代のトランジスタを狙う非シリコン材料(4)〜CMOSの実現手法と試作例:福田昭のデバイス通信(36)(2/3 ページ)

» 2015年08月07日 11時30分 公開

[福田昭,EE Times Japan]

n型InGaAsとp型SiGeのCMOSリング発振器が動作

n型FETにInGaAsチャンネル、p型FETにGeチャンネルを採用するCMOSデバイスの研究では、簡単なICを試作して動作速度を測定する成果が出ている。2014年6月に国際会議VLSIシンポジウムで、産業技術総合研究所(産総研)がCMOSリング発振器を試作したと発表した。

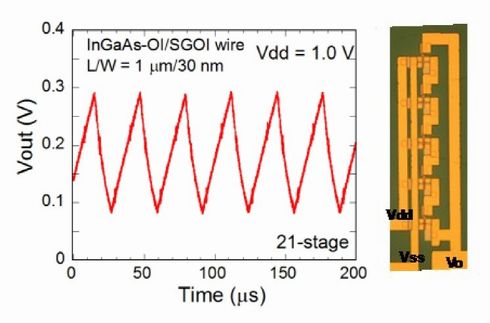

産総研が試作したのは、21段のCMOSリング発振器である。電源電圧が1.0Vのときに、遅延時間が約35μs/段の速度で動作した。それほど高速であるとは言えないが、初期試作の段階であることを考慮すると、良好な値だとも言える。

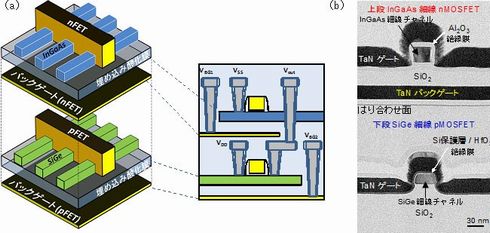

CMOS構造の作成方法は以下の通り。SiGe FETをSiウエハー上に形成した後で、InGaAs層を成膜済みのInPウエハーをSiウエハーにフェース・ツー・フェースで貼り合わせる。続いてInP層を取り除く。それからInGaAs FETを形成する。こうすると、p型SiGe MOS FETの上に、n型InGaAs MOS FETを積層したCMOS構造が出来上がる。

なお産総研は、上記の手法でp型Ge MOSFETの上にn型InGaAs MOSFETを積層したCMOSインバータ論理ゲートを試作し、2013年6月に国際学会VLSIシンポジウムでその概要を発表している。この発表が、InGaAs FETとGe FETのCMOSデバイスを初めて製造した研究成果である。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

Special SitePR

あなたにおすすめの記事PR