HBM 2対応メモリを統合、アルテラのFPGA:メモリ帯域幅を従来比10倍以上に拡大

アルテラは、同社のハイエンドFPGA製品とSK Hynix製3D積層メモリチップを統合したヘテロジニアスSiP(System in Package)デバイス「Stratix 10 DRAM SiP」を発表した。DRAMを外付けしていた場合に比べ、メモリ帯域幅は最低10倍となる。

アルテラは2015年11月、同社のハイエンドFPGA製品とSK Hynix製3D積層メモリチップを統合したヘテロジニアスSiP(System in Package)デバイス「Stratix 10 DRAM SiP」を発表した。DRAMを外付けしていた場合に比べ、メモリ帯域幅は最低10倍となる。

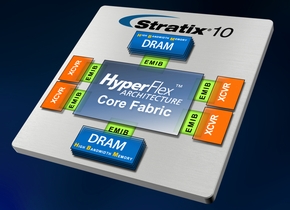

Stratix 10 DRAM SiPは、最新のFPGA「Stratix 10 FPGA&SoC」と、SK Hynix製「HBM(High Bandwidth Memory) 2 対応スタックメモリ」を統合した製品となる。これらの技術を組み合わせることで、これまでシステム性能の改善に向けて課題となっていたメモリ帯域幅によるボトルネックを解消しつつ、高い電力効率を達成することができるという。

ヘテロジニアスSiP製品には、IntelのEMIB(Embedded Multi-die Interconnect Bridge)技術が用いられている。この技術により、シリコンブリッジを用いて1つのパッケージ内で複数のベアチップを相互接続することができる。従来の、インタポーザベースの接続手法に比べて、高い性能を実現しつつ実装の簡素化やコストの節減なども可能となる。

SK HynixのHBM 2対応スタックメモリは、複数のDRAMチップを垂直に重ね、シリコン貫通電極(TSV)とマイクロバンプを用いて相互接続した製品である。256Gバイト/秒のメモリ帯域幅を実現しつつ、電力消費を66%低減することが可能だという。

今回のStratix 10 DRAM SiPでは、DRAMメモリチップとFPGAチップをできる限り近くに配置することが可能となる。このため、極めて短い配線長と広いメモリ帯域幅でチップ同士を接続することができ、消費電力も少なく抑えることが可能となった。

Stratix 10 DRAM SiP製品の出荷開始は2017年を予定している。データセンター用システムや放送機器、通信ネットワーク装置及び、高性能コンピュータ機器など、データ処理量が増加している用途に向ける。

関連記事

アルテラのStratix10、新アーキテクチャ採用で従来比2倍のコア性能

アルテラのStratix10、新アーキテクチャ採用で従来比2倍のコア性能

アルテラは、ハイエンドのプログラマブルロジックデバイス「Stratix10FPGA&SoC」のアーキテクチャと製品概要を発表した。新製品は「HyperFlexアーキテクチャ」や「ヘテロジニアス3D SiP(System in Package)インテグレーション」技術を採用している。製造はIntelの14nmトライゲートプロセスを用いて行われる。 インテルがアルテラを167億ドルで買収へ

インテルがアルテラを167億ドルで買収へ

IntelがAlteraを167億米ドル(約2兆円)で買収する。2015年4月には、買収の交渉が決裂したと報じられたが、その後、合意にこぎつけたようだ。 アルテラが20nm SoC FPGAを出荷開始、性能は50%向上

アルテラが20nm SoC FPGAを出荷開始、性能は50%向上

アルテラは、20nmプロセス技術を用いて製造する第2世代SoC(System on Chip) FPGA「Arria 10 SoC」の出荷を開始した。前世代製品に比べて、処理性能を最大50%向上し、消費電力は最大40%削減できるという。 TSMCとAlteraが新パッケージ技術を開発――フラッシュ混載FPGA「MAX 10」向け

TSMCとAlteraが新パッケージ技術を開発――フラッシュ混載FPGA「MAX 10」向け

TSMCとAlteraは、Alteraの55nmフラッシュメモリを混載したFPGA「MAX 10 FPGA」(以下、MAX 10)向けに最適化した新しいパッケージング技術を共同で開発したと発表した。厚さ0.5mm以下の薄型パッケージを実現したという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

1つのパッケージ内で複数のベアチップを相互接続することができるヘテロジニアスSiP製品のイメージ図 出典:アルテラ

1つのパッケージ内で複数のベアチップを相互接続することができるヘテロジニアスSiP製品のイメージ図 出典:アルテラ