不揮発性メモリを脳神経コンピューティングに活用:福田昭のデバイス通信 IEDM 2015プレビュー(7)(3/3 ページ)

» 2015年11月17日 09時50分 公開

[福田昭,EE Times Japan]

接触ギャップが5nmと微小なナノサイズのリレー

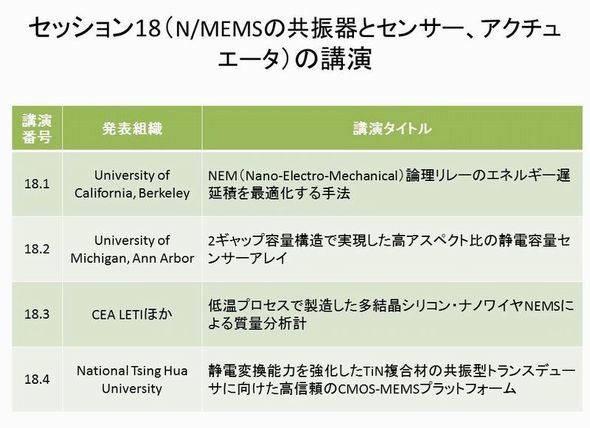

セッション18(プロセス技術と製造技術)のテーマは「N/MEMSの共振器とセンサー、アクチュエータ」である。テーマの通り、極めて微小な電気機械素子の研究成果が続出する。

University of California, Berkeleyは、ナノメートルサイズの論理リレー(NEMロジックリレー)でエネルギー遅延時間積を最適化する手法を提唱する(講演番号18.1)。一般的にはリレーの硬さを減らすことがスイッチング・エネルギーの最小化に結び付く。この研究ではリレーのバネ定数を相対的に大きくすることでスイッチング・エネルギーを小さくした。接触ギャップがわずか5nmと小さなNEMロジックリレーでエネルギー遅延時間積を最適化して見せる。

Tsinghua Universityは、共振周波数が最大14GHzと高い表面弾性波(SAW)トランスデューサを試作し、その概要を発表する(講演番号18.6)。トランスデューサの材料はニオブ酸リチウム(LiNbO3)、配線幅は30nmと極めて細い。

Korea Advanced Institute of Science and Technology (KAIST)を中心とする研究チームは、多孔質の高分子フィルムを摩擦電気エネルギーの収穫素子に活用することを提案する(講演番号18.7)。多孔質層を摩擦帯電層としたときの出力特性を解析した。

(次回に続く)

⇒「福田昭のデバイス通信」バックナンバー一覧

関連記事

ナノワイヤと非シリコン材料で「ムーアの限界」を突破

ナノワイヤと非シリコン材料で「ムーアの限界」を突破

今回はセッション13〜15の概要を取り上げたい。セッション15では、「モア・ムーア(More Moore)」と「モアザン・ムーア(More Than Moore)」の両方に関する研究成果が発表される。「モアザン」については、フランスの研究チームが折り曲げ可能なCMOS回路を紹介する。 IoT向けSoCでは、ムーアの法則を追わず

IoT向けSoCでは、ムーアの法則を追わず

コストと性能のバランスが最も重視されるIoT機器に搭載されるSoCでは、最先端のプロセスを適用することは必ずしも最善の策ではない。 3D NANDフラッシュの物理解析が進む

3D NANDフラッシュの物理解析が進む

今回はセッション4〜6の講演を紹介する。セッション4では、人間の脳をモデルにした計算アーキテクチャなどが焦点となる。セッション5では3D NAND型フラッシュメモリ関連の発表が行われ、セッション6ではIGZO材料による20nmノードの高周波FETなどが発表される予定だ。 革新的な磁気メモリ材料の発見か

革新的な磁気メモリ材料の発見か

東京大学物性研究所の中辻知准教授らの研究グループは2015年10月29日、反強磁性体において異常ホール効果を「世界で初めて観測した」と発表した。同研究グループは高密度/高速な不揮発性メモリ素子の実現につながる発見としている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- デンソー、ロームに対する株式取得提案を正式表明

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- 次世代パワー半導体 「期待の5材料」の現在地――電子版2026年3月号

Special SitePR

あなたにおすすめの記事PR