TSMCが5nmプロセス開発に着手:EUVの採用は、まだ不明

TSMCが5nmプロセスの開発に着手する。ただし、EUV(極端紫外線)リソグラフィを採用するかどうかは、まだ不明だ。とはいえ、193nm ArF液浸リソグラフィを適用するには、かなりの数のパターニングが必要になり、コストが膨れ上がる。

EUVの適用は、まだ分からず

世界最大のファウンドリであるTSMCは、5nmプロセス技術の開発に着手し、先端技術開発をさらに推し進める考えであることを明らかにした。ただし同社は、5nmプロセスにおいてEUV(極端紫外線)リソグラフィ装置を使用するかどうかについては、まだ判断しかねているという。

同社の共同CEOであるMark Liu氏は、台湾の新竹(Hsinchu)で2015年12月初めに行われたサプライチェーン経営会議において、今回の5nmプロセス技術開発についてコメントしている。同氏によると、「当社としては、製品ロードマップにおける5nmプロセスの位置付けをまだ決められずにいる。プロセスの一部でEUVリソグラフィ装置を使用すべきかどうか、現在も検討しているさなかだ」という。

TSMCが5nmプロセスの初期開発に着手したということは、EUVは液浸リソグラフィの代替技術にはならないという可能性を示唆しているのではないだろうか。ASMLは、EUVを推進しているが、競合のニコンは、193i(波長193nmのArF液浸リソグラフィ)技術を推進している。

これまでにさまざまな試験が行われた結果、半導体業界がムーアの法則をさらに進めるべく5nmプロセスを実現するには、193iとEUVとを組み合わせるのが最善策であることが明らかになっている。TSMCは、10nmプロセス技術にはトリプルパターニングが必要だとしている。

193iのみを適用する場合、金属膜にはクアッドパターニングが、ビアにはトリプルパターニングがそれぞれ必要なため、コストが非常に高くなる。一方EUV技術では、必要な膜数が少なくて済み、消費電力や性能などの面でも液浸リソグラフィに勝っているが、EUV装置そのものがまだ開発途上にあるため、実用化には程遠い。

193iでは8回のパターニングが必要に

193iを7nm以降へと適用することも可能だが、8回パターニングするオクタプルパターニングが必要となる他、ステップも追加しなければならないため、製造コストが増加する。こうした点が、微細化を進める半導体メーカーの勢いを減速させる要因となり、さらには半導体業界全体の成長を低迷させる可能性もある。

IBM Researchは2015年に、7nmプロセス技術開発において、EUVリソグラフィ技術を採用し、FinFETトランジスタにSiGe(シリコンゲルマニウム)チャネルを使うことで、Intelを超える成果を挙げている。これにより、IBMの開発パートナーであるSamsung Electronicsも、2018年には7nmプロセス適用製品を実現できる見込みであると発表するなど、Intelに追い付くための競争において後押しを受ける形となった。

TSMCは2015年10月、7nmプロセスを適用した完全動作SRAMを開発したと発表し、2017年には最初の7nmプロセス適用製品を出荷できる見込みであることを明らかにした。また、2015年第4四半期中には10nmプロセス品の認定作業(クオリフィケーション)を開始し、2016年初めには顧客企業向けにテープアウトできる予定だという。また、同社は2015年9月、出力90WのEUV装置の開発について進ちょくを報告している。2015年内には、1時間当たり125枚のウエハーを処理できる性能を実現する見込みだという。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

IBMが7nm試作チップを発表、Intelに迫る勢い

IBMが7nm試作チップを発表、Intelに迫る勢い

IBM Researchが、EUV(極端紫外線)リソグラフィとSiGe(シリコンゲルマニウム)チャネルを使用した7nmプロセス試作チップを発表した。IBM Researchはここ最近、最先端プロセスの研究開発成果の発表に力を入れていて、7nmプロセスの技術開発に自信を示してきたIntelに迫る勢いを見せている。 ASMLがEUVリソグラフィ開発の最新状況を公表(1)〜ArF液浸の限界

ASMLがEUVリソグラフィ開発の最新状況を公表(1)〜ArF液浸の限界

今回は、コストとパターン形成の2点について、ArF液浸とEUV(極端紫外線)リソグラフィを比べてみよう。ArF液浸では、10nm世代になるとステップ数と重ね合わせ回数が破壊的な数値に達してしまう。これがコストの大幅な上昇を招く。さらに、ArF液浸とEUVでは、10nm世代の配線パターンにも大きな差が出てくる。 ARMから見た7nm CMOS時代のCPU設計(1)

ARMから見た7nm CMOS時代のCPU設計(1)

ARMにとって「IEDM」は非常に重要だ。この会議で議論されるトランジスタ技術が同社のCPUアーキテクチャの行方を左右するからである。ARMは「IEDM 2014」で、CPU設計とデバイス・プロセス技術の関わりを解説する講義を行った。今回から、その内容を複数回にわたってお届けする。 ナノワイヤと非シリコン材料で「ムーアの限界」を突破

ナノワイヤと非シリコン材料で「ムーアの限界」を突破

今回はセッション13〜15の概要を取り上げたい。セッション15では、「モア・ムーア(More Moore)」と「モアザン・ムーア(More Than Moore)」の両方に関する研究成果が発表される。「モアザン」については、フランスの研究チームが折り曲げ可能なCMOS回路を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

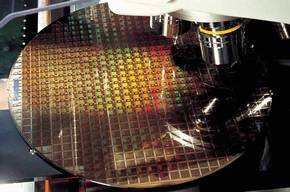

TSMCで製造しているウエハー 出典:TSMC

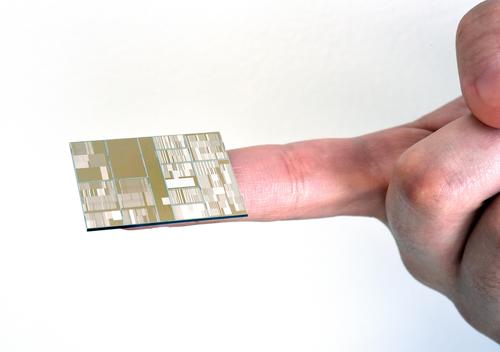

TSMCで製造しているウエハー 出典:TSMC IBMが試作した7nmチップの外観 出典:Darryl Bautista/Feature Photo Service for IBM

IBMが試作した7nmチップの外観 出典:Darryl Bautista/Feature Photo Service for IBM