超高密度のSRAM技術と超広帯域のDRAM技術:福田昭のデバイス通信 ISSCC 2016プレビュー(6)(2/2 ページ)

307Gバイト/秒の超広帯域転送を可能にしたHBM2 DRAM

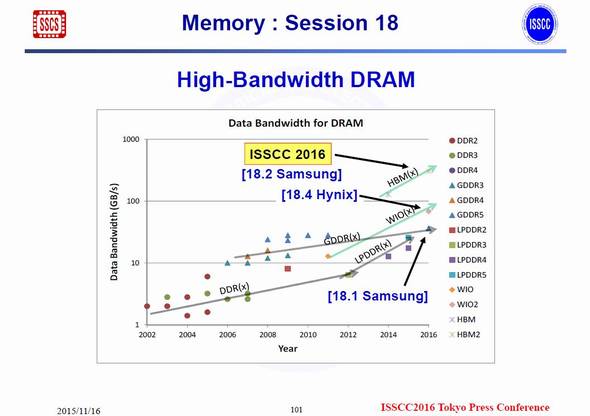

セッション17に続いて開催されるセッション18のメインテーマは「メモリ」、サブテーマは「広帯域DRAM」である。このセッションでは、データ転送速度を200Gバイト/秒〜300Gバイト/秒に高めたHBM(High-Bandwidth Memory) DRAM技術の発表が相次ぐ。

Samsung Electronicsは、データ転送速度が307Gバイト/秒と高いHBM2 DRAM技術を発表する(講演番号18.2)。製造技術は20nmのCMOS、電源電圧は1.2Vである。HBMは最大で8枚のDRAMシリコンダイを積層する。ウエハーレベルで実動作速度で検査可能なテスト回路と、複数のオンチップ温度センサーと連動したリフレッシュ制御回路を内蔵する。

SK Hynixは、データ転送速度が256Gバイト/秒のHBM DRAM技術を報告する(講演番号18.3)。記憶容量は64Gビット(8Gビットのシリコンダイを8枚積層)、入出力チャンネルは8チャンネル、電源電圧は1.2Vである。

この他、入出力ピン当たりのデータ転送速度が9Gビット/秒と高いGDDR5 DRAM技術をSamsung Electronicsが発表する(講演番号18.1)。記憶容量は8Gビット、製造技術は20nmである。NBTI劣化のモニター回路とジッタの低減回路、分散電源回路を搭載した。

SK Hynixは、2014年9月に開発を明らかにしたWide-IO2 DRAM*)の技術概要を報告する(講演番号18.4)。データ転送速度は68.2Gバイト/秒と高い。記憶容量は8Gビットである。電源電圧は1.1V。

*)関連記事:SKハイニックス、次世代モバイル用DRAM「Wide I/O 2」を開発――20nmプロセス採用

(次回に続く)

関連記事

Micronが苦戦、PC市場低迷の影響で

Micronが苦戦、PC市場低迷の影響で

2015年度第4四半期の業績を発表したMicron Technology。売上高は3四半期連続で減少していて、同社が苦戦している様子がうかがえる。「Windows 10」が発表されてもPC市場の低迷は止まらず、その影響を受けているとみられる。 印刷技術で、有機強誘電体メモリの3V動作を確認

印刷技術で、有機強誘電体メモリの3V動作を確認

産業技術総合研究所の野田祐樹氏らは、低電圧でも動作する有機強誘電体メモリの印刷製造技術を開発した。この技術を用いて作成した薄膜素子は、電圧3Vでメモリ動作することを確認した。 次世代メモリ市場、2020年には70億米ドル規模に

次世代メモリ市場、2020年には70億米ドル規模に

ReRAMやMRAMといった不揮発RAM市場は、今後急成長を遂げ、2020年には70億米ドル規模に拡大すると見られている。NAND型フラッシュメモリやDRAMに取って代わるには、微細化とビット当たりの価格が鍵になりそうだ。 2015年の半導体製造装置市場、7%成長へ

2015年の半導体製造装置市場、7%成長へ

SEMIは2015年年央における、2015年の半導体製造装置市場が前年比7.1%増の401.5億米ドルになるとの予測を発表した。販売額増加をけん引するのは、メモリおよびファウンドリとみている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増