キャッシュメモリの基礎:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(6)(3/3 ページ)

» 2016年03月04日 11時30分 公開

[福田昭,EE Times Japan]

実用的な構造は「セットアソシアティブ方式」

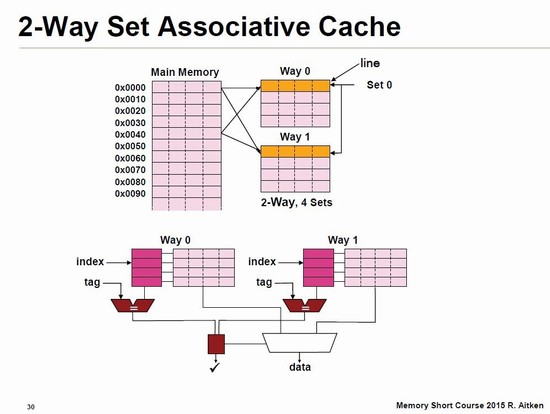

そこで、フルアソシアティブ方式とダイレクトマッピング方式の中間的な方式である「セットアソシアティブ(Set Associative)方式」が、ほとんどのCPUアーキテクチャが採用するキャッシュ構造となっている。

セットアソシアティブ方式では、インデックスを利用してマッピングするという点では、ダイレクトマッピング方式と変わらない。ただし、同じインデックスに対応するキャッシュラインを複数個、用意する。最も単純な構造では、同じインデックスに対して2個のキャッシュラインを準備しておく。この同じインデックスに対応するキャッシュラインのグループを「ウエイ」と呼ぶ。そしてウエイの数に応じてグループを特定する。例えば2個のキャッシュラインを同じインデックスに用意した場合は「2ウエイ」となり、1つのグループを「ウエイ0」、もう1つのグループを「ウエイ1」と呼んで区別する。なおウエイ数は2個(2ウエイ)とは限らない。4ウエイ、8ウエイといったキャッシュ構造も採用されている。

具体的なキャッシュアクセス動作は以下のようになる。CPUがアクセス要求を出したアドレスからは、まずインデックスに対応するラインを探す。当然ながらウエイ数と同じだけの候補が見つかる。あるいは、対応するラインが見つからない(「キャッシュミス」、あるいは「ミス」と呼ぶ)。候補が見つかった場合は、上位アドレスの違いから、どのウエイのラインが対応するか、あるいはどのウエイのラインも対応していないかを判断する。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

2019年までのストレージ市場を展望する(前編)

2019年までのストレージ市場を展望する(前編)

米国のストレージ専門調査会社TRENDFOCUSは、2015年5月に東京で開催された「DiskCon Japan 2015」で、ストレージ市場の最新状況を解説するとともに、2019年までの市場動向を展望した。今回は、ハードディスク装置(HDD)の市場動向に関する講演内容を紹介する。 東芝、3D NAND製造用に四日市工場の敷地を拡張

東芝、3D NAND製造用に四日市工場の敷地を拡張

東芝は、3次元NAND型フラッシュメモリの製造に向け、四日市工場の敷地を拡張すべく、同工場の隣接地を取得すると発表した。 メモリの薄化限界は4μm! 2μm台で劣化を確認

メモリの薄化限界は4μm! 2μm台で劣化を確認

東京工業大学とWOWアライアンスは2015年12月15日、300mmシリコンウエハーの厚さを2μmにすることで、DRAMの特性が劣化することを確認し、シリコンウエハーの薄化は4μm程度が実用的であるとの研究成果を発表した。 ルネサス、自動運転車向けSoC用高速SRAMを開発

ルネサス、自動運転車向けSoC用高速SRAMを開発

ルネサス エレクトロニクスは2015年12月9日、16nm世代以降の先端プロセスを採用する車載情報機器用SoC(System on Chip)に内蔵するための高速SRAMを開発したと発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR