SRAMの書き込み動作を理解する:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(15)(2/2 ページ)

» 2016年04月11日 09時30分 公開

[福田昭,EE Times Japan]

ワード線のパルス電圧には一定の長さが必要

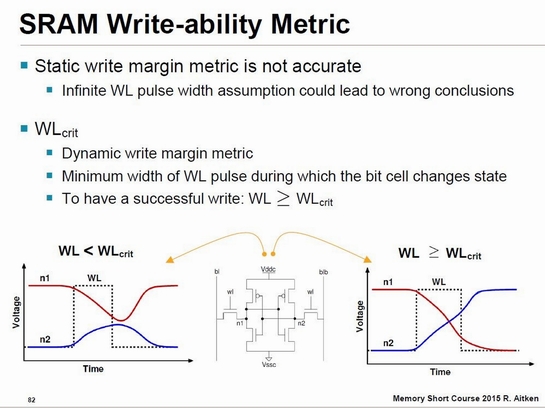

ワード線の選択では、選択したワード線の電位を一定の期間だけ高い電位に持ち上げ、再び低い電圧に下げる(「ワード線パルス」あるいは「WLパルス」)。このワード線パルスがある期間よりも短くなると、SRAMセルの値は反転せずに、元に戻ってしまう。この境界(クリティカルな期間)を「WLcrit」と呼ぶ。

適切な書き込み動作を実現するためには、ワード線パルス(WLパルス)の時間幅はWLcritよりも長くしなければならない。

SRAMを構成する要素のタイミングばらつき

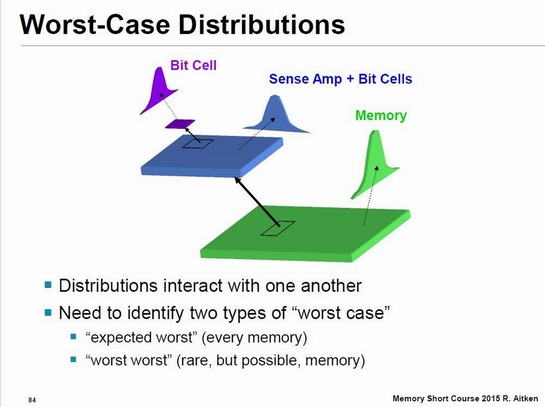

SRAMを構成する要素であるメモリセル(ビットセル)やセンスアンプなどには、当然ながらタイミングのばらつきが存在する。

メモリセル、クロック、アドレスデコーダー、ワード線ドライバ、ビット線ドライバ、センスアンプといった各要素のタイミングのばらつきは、独立に存在するとは限らない。相互に影響し合うこともある。

重要なのは最悪の場合(ワーストケース)の扱いだ。通常は、2つのケースを扱う。1つは、各要素のばらつきをランダムな存在と仮定したワーストケースである。このワーストケースでは、設計値(あるいは中央値)からのずれがそれほど大きくはならない。実際のSRAMでも、大抵の場合はこの範囲に収まる。

もう1つは、各要素のばらつきが加算されていった結果としてのワーストケースである。この場合、設計値(あるいは中央値)からのずれが非常に大きくなる。このようなワーストケースが発生する確率は非常に低い。まれな事象ではあるが、考慮しておく必要はある。

(次回に続く)

関連記事

SRAMの基本要素とレイアウト

SRAMの基本要素とレイアウト

今回からはSRAMについて知っておくべきことを紹介していく。まずは、多くの半導体メモリにも共通するSRAMシリコンダイの基本レイアウトから説明していこう。 DRAMについて知っておくべき、4つのこと

DRAMについて知っておくべき、4つのこと

今回は、DRAMで知っておくべき4つの事実を紹介する。「DRAMの事業規模は巨大であること」「DRAMの性能は常に不足していること」「DRAM開発は傾斜が急になり続ける坂道を登っているようなものであること」「3次元技術はDRAM開発にとって援軍ではあるが救世主ではないこと」の4つだ。 14/16nm世代のSRAMと第3の2Dデバイス材料

14/16nm世代のSRAMと第3の2Dデバイス材料

今回のプレビューでは、セッション10〜12の内容を紹介する。セッション11では、ルネサス エレクトロニクスやSamsung ElectronicsがSRAM関連の技術を発表する。セッション12では、第3の2Dデバイス材料として注目を集める黒リン関連の発表に注目したい。 インテル、14nm SRAMの実現へ

インテル、14nm SRAMの実現へ

Intelは、「ISSCC 2015」において14nmプロセスのSRAMについて論文を発表する予定だ。同社のシニアフェローはムーアの法則についても言及し、「ムーアの法則は10nm以降も継続する。EUV(極端紫外線)リソグラフィ技術を採用せずに7nmプロセス技術を実現できれば、トランジスタ当たりのコストを削減できる」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR