インテル、14nm SRAMの実現へ:ISSCC 2015(1/3 ページ)

Intelは、「ISSCC 2015」において14nmプロセスのSRAMについて論文を発表する予定だ。同社のシニアフェローはムーアの法則についても言及し、「ムーアの法則は10nm以降も継続する。EUV(極端紫外線)リソグラフィ技術を採用せずに7nmプロセス技術を実現できれば、トランジスタ当たりのコストを削減できる」と述べている。

Intelは、米国サンフランシスコで開催中の半導体集積回路技術の国際会議「ISSCC(IEEE International Solid-State Circuits Conference)2015」(2015年2月22〜26日)で、業界最小クラスをうたうDRAMおよびI/O回路について発表する予定だという。これにより、同社の14nmプロセス技術を実証したい考えだ。ISSCC 2015では論文のプレビューが行われているが、その中でIntelの経営幹部は、同社が10nm/7nm世代のプロセス技術に向けた取り組みについて、楽観的な見方をしているとする主張を繰り返した。

Intelが発表を予定しているのは、1mm2当たり14.5Mビットのデータ保存が可能な、0.0500μm2 SRAMビットセルだ。14nmプロセスを適用し、0.6V時の動作周波数は最大1.5GHzだという。

同社のフェローであるKevin Zhang氏は、「このセルは、メモリアレイの一部として機能する。Intelが今後発表予定のSoCに広く採用する予定だ。例えば、1つのダイで数百Mビットを使うセルラーモデムなどが挙げられる」と述べている。

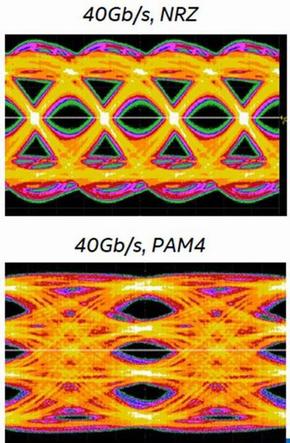

40Gbpsを実現する14nm SerDesも

またIntelは、別の論文の中で、14nmプロセスを適用したSerDes(シリアライザ/デシリアライザ)トランスミッタについても発表する予定だ。変調方式は、NRZ(Non Return to Zero)またはPAM-4(4値パルス振幅変調)のいずれかを採用することにより、最大40Gビット/秒の信号速度を実現するという。0.03mm2で25Gビット/秒を超える性能を提供することが可能な、「世界最小クラスのトランスミッタである」としている。

さらに別の論文では、14nmプロセスを適用した、PCI Express(PCIe)向け10Gビット/秒シリアルリンクについても発表する。消費電力量はわずか59mW、シリコン面積は0.065mm2だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- Cerebrasが上場 NVIDIA対抗馬の「試金石」となるか

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk