0.03μm2のSRAMから最先端のIII-V族FinFETまで:「VLSI技術シンポジウム 2016」プレビュー(3/5 ページ)

新チャネル材料と、新デバイス構造

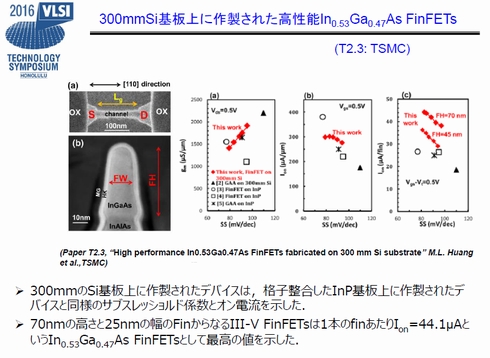

TSMCは、300mmのシリコン基板上に、InGaAs(インジウム・ガリウム・ヒ素)の結晶を成長させ、そこにFinFETを形成した。300mmのシリコン基板の全域にFinFETを形成し、全域にわたり評価をしている。これまでの研究開発では、InGaAs FinFETはInP(インジウム・リン)基板の上に作成されることが多かった。InGaAsとInPの結晶構造が似ているので、InGaAsの結晶が成長しやすいからだ。ただ、InP基板は非常に高価という点が課題だった。

今回の研究でTSMCは、シリコン基板上に作成したInGaAs FinFETは、InP基板上に作成したInGaAs FinFETと、ほぼ同等レベルの特性を示すことを確認したという。具体的には、高さ70nm、幅25nmのフィンを持つFinFETは、フィン1本当たりのオン電流が44.1μAだったという。InP基板を使うよりも安価に、高性能なInGaAs FinFETを実現できることを示した。

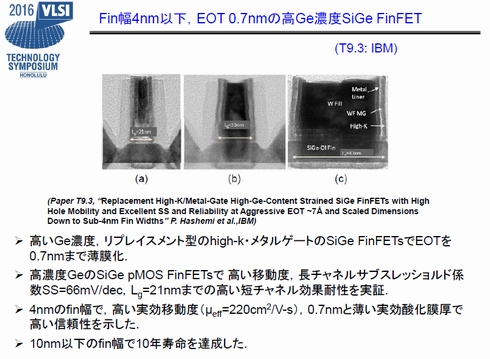

IBMは、フィン幅がわずか4nm、EOT(Equivalent Oxide Thickness)が0.7nmのSiGe FinFETを発表する。Geの濃度が非常に高いSiGe基板から、リプレイスメント型のhigh-k/メタルゲートを使い、FinFETを作成した。このプロセスでpMOS FinFETを作成し、評価をしたところ、ゲート長21nmの短チャネル効果耐性と、220cm2/V-sという高い正孔移動度を達成したという。

IMECは、シリコンナノワイヤを2本、縦に積層したトランジスタを発表する。具体的には、急速溶融成長(RMG)プロセスを用いた直径8nmのGAA(Gate-All-Around) nFET、同pFETを縦方向に積層した。このように積層することで、面積当たりの電流を増やすことができる。IMECが開発したこのナノワイヤは、ゲート長24nmという優れた短チャネル効果耐性を持つという。

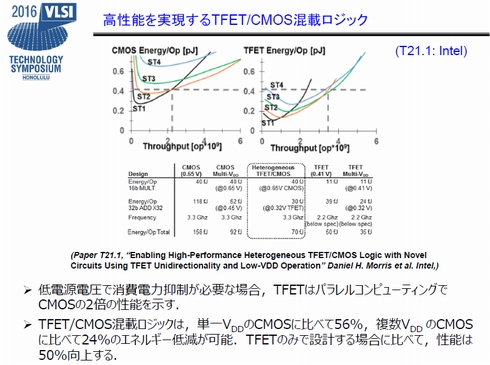

Intelは、トンネルFET(TFET)とCMOSの混載ロジックを発表する。同混載ロジックでは、単一電源電圧のCMOSに比べてエネルギー効率を56%削減でき、複数の電源電圧を使い分けるCMOSに比べて24%削減できることを、シミュレーションによって実証したとしている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk