0.03μm2のSRAMから最先端のIII-V族FinFETまで:「VLSI技術シンポジウム 2016」プレビュー(5/5 ページ)

» 2016年04月25日 08時30分 公開

[村尾麻悠子,EE Times Japan]

3D集積化技術

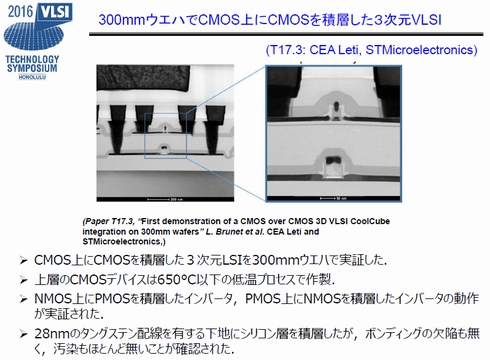

フランスCEA LetiとSTMicroelectronicsは、300mmウエハー上で、CMOSにCMOSを積層する3次元(3D)LSIを発表する。上層のCMOSデバイスは、下層のCMOSデバイスの特性に影響を与えないよう、650℃以下の低温プロセスで作成されている。NMOS上にPMOSを積層したインバーターおよび、PMOS上にNMOSを積層したインバーターの動作を実証したとする。さらに、28nmのタングステン配線を下地に設け、その上に上層CMOSデバイスを作成したとしても、ボンディングなどで欠陥は生じず、汚染もほぼないことを確認したという。

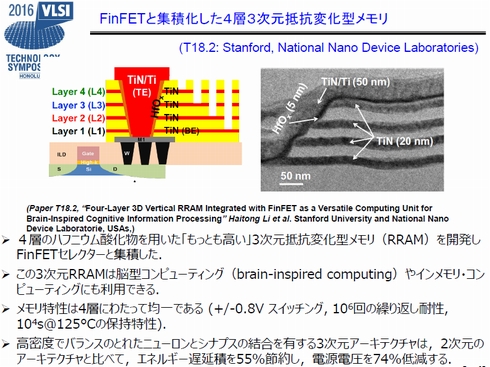

米国スタンフォード大学は、抵抗変化型メモリ(RRAM)を積層した3D RRAMを発表する。FinFETの上に4層のハフニウム酸化物を集積している。メモリ特性は4層にわたり均一になっている。スタンフォード大学は、この3次元RRAMを脳型コンピューティングやインメモリ・コンピューティングにも利用できるとしている。3次元に積層することで、2次元に比べて電源電圧を74%低減できるという。

関連記事

10nmプロセス以降に焦点、“微細化のその先”も

10nmプロセス以降に焦点、“微細化のその先”も

2016年6月に米国ハワイで開催される「2016 VLSI Symposia on VLSI Technology and Circuits」では、10nm以降のプロセス技術の研究成果も多数発表される予定だが、“微細化のその先”についても、これまで以上に活発な議論が行われるようだ。 STT-MRAMの基礎――情報の蓄積に磁気を使う

STT-MRAMの基礎――情報の蓄積に磁気を使う

次世代不揮発メモリの候補の1つに、STT-MRAM(スピン注入磁化反転型磁気メモリ)がある。データの読み書きが高速で、書き換え可能回数も多い。今回から始まるシリーズでは、STT-MRAMの基本動作やSTT-MRAが求められている理由を、「IEDM2015」の講演内容に沿って説明していこう。 ARMから見た7nm CMOS時代のCPU設計(1)

ARMから見た7nm CMOS時代のCPU設計(1)

ARMにとって「IEDM」は非常に重要だ。この会議で議論されるトランジスタ技術が同社のCPUアーキテクチャの行方を左右するからである。ARMは「IEDM 2014」で、CPU設計とデバイス・プロセス技術の関わりを解説する講義を行った。今回から、その内容を複数回にわたってお届けする。 “次世代メモリ”の域を出ないFRAM、量産規模を上げて低価格化を

“次世代メモリ”の域を出ないFRAM、量産規模を上げて低価格化を

SRAMやDRAM、EEPROMを置き換えるとして大いに期待されていたFRAMは、量産こそ始っているものの、完全に普及しているとはいえず、いまだに“次世代メモリ”の域を出ない。だが、一定のニーズはある。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

Special SitePR

あなたにおすすめの記事PR