毎秒56Gビットの無線伝送、CMOS回路で実現:ワイヤレスジャパン/WTP 2016

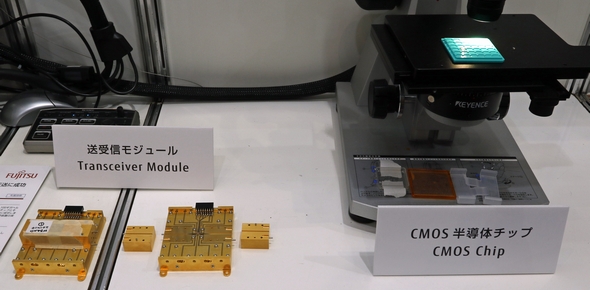

富士通は、「ワイヤレス・テクノロジー・パーク(WTP)2016」で、富士通研究所と東京工業大学が開発した、毎秒56Gビットの無線伝送を可能とするCMOS無線送受信チップとそのモジュール技術を紹介した。

富士通は、「ワイヤレス・テクノロジー・パーク(WTP)2016」(2016年5月25〜27日、東京ビッグサイト)で、富士通研究所と東京工業大学が開発した、毎秒56Gビットの無線伝送を可能とするCMOS無線送受信チップとそのモジュール技術を紹介した。

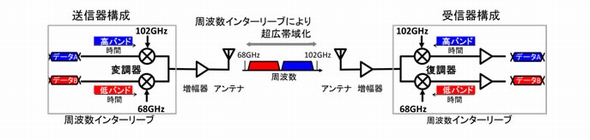

開発したCMOS無線送受信チップは、データ信号を2つに分けて、それぞれ異なる周波数帯に変換してから混合することで、送受信回路を広帯域化、低損失化する技術を用いた。具体的には、低い帯域の信号は72〜82GHz、高い帯域の信号89〜99GHzに分けた。これをそれぞれ10GHz幅ごとに変復調を行う。この技術を用いることで、20GHz帯域幅の信号も高品質で伝送することを可能にしたという。

ミリ波帯の信号を電波で送受信するための増幅器も開発した。増幅率は周波数によって部分的に低下する信号成分がある。これに対して、出力信号の振幅を入力側へフィードバックして増幅率を安定化させる回路技術を開発。72〜100GHzと極めて帯域が広い増幅器を実現できたという。「半導体チップは65nmCMOSプロセス技術を用いて製造した」(説明員)と話す。

ミリ波帯通信などに用いる半導体チップは、実装するためのモジュール技術が伝送特性などに大きく左右する。富士通研究所は、プリント配線板上の配線パターンを工夫することで、インピーダンスマッチングさせた導波管と基板とのインタフェースを開発し、大幅な損失低減を図った。

富士通研究所では、試作した2台のモジュールを10cmの距離で対向させて設置し、データ伝送試験を行った。導波管と基板の間の損失を10%以下に抑え、毎秒56Gビットのデータ転送に成功したという。

今回開発した技術は、光ファイバー通信網を補完する技術と位置付けている。光ファイバーの敷設が困難な用途/地域において、大容量無線通信を実現していく。毎秒56Gビットの無線伝送容量があれば、8Kの超高精細映像を非圧縮かつ、リアルタイムに無線伝送することが可能だという。

同社では、2020年ごろの実用化を目指している。今後は、伝搬距離を伸ばすために出力が1W級のパワーアンプ開発なども併せて行っていく計画だ。

関連記事

AllJoynでBluetoothが使える! ルネサスがデモ

AllJoynでBluetoothが使える! ルネサスがデモ

ルネサス エレクトロニクスは、「ワイヤレスジャパン 2016」(2016年5月25〜27日、東京ビッグサイト)で、AllJoyn対応機器をBluetooth Low Energy(BLE)で相互接続するデモを披露した。AllJoynでBLEを使用するのは「業界初」(同社)だという。 IoT機器向けマルチプロトコルSoC、Sigfox対応へ

IoT機器向けマルチプロトコルSoC、Sigfox対応へ

シリコン・ラボラトリーズは、「ワイヤレスジャパン2016」(2016年5月25〜27日/東京ビッグサイト)で、IoT機器向けマルチプロトコルSoC「Wireless Gecko EFR32」シリーズを展示した。 地球規模で膨大なセンサー端末を無線でつなぐ

地球規模で膨大なセンサー端末を無線でつなぐ

リニアテクノロジーは「ワイヤレスジャパン2016」で、無線ネットワーク技術「dust networks(ダスト・ネットワークス)」の採用事例などを展示した。また、巨大な無線センサーネットワークの構築を可能とする「ネットワークマネージャ」についてもその概要を紹介した。 5G実現にまた一歩、73GHz帯で8K映像を伝送

5G実現にまた一歩、73GHz帯で8K映像を伝送

NTTドコモと、Nokiaの日本法人であるノキアソリューションズ&ネットワークス(以下、ノキア)は、現在開催中の「ワイヤレス・テクノロジー・パーク(WTP) 2016」で、73.5GHz帯を使用して8K映像をリアルタイムで伝送するデモを披露した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

展示した送受信モジュールとCMOS半導体チップ

展示した送受信モジュールとCMOS半導体チップ 開発した送受信機の構成イメージ 出典:富士通

開発した送受信機の構成イメージ 出典:富士通