EE Times Japan >

プロセス技術 >

EUVは、微細化の“万能策”ではない:「ITF 2016」で語られた半導体の未来(2)(2/2 ページ)

» 2016年06月09日 09時30分 公開

[Rick Merritt,EE Times]

チップの80%は最先端のものではない

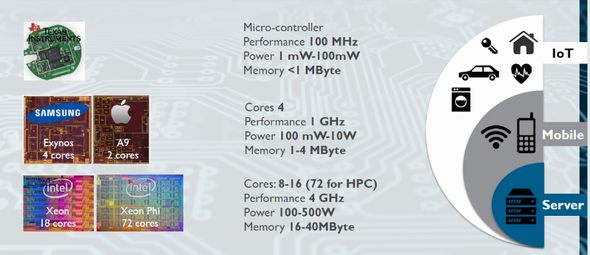

最先端チップの製造コストが増加していることや、エレクトロニクス市場で多様性が増していることから、半導体の開発ロードマップは広がりを見せている。

GLOBALFOUNDRIESは、それを示す事例を紹介した。同社は、低コストなプレーナ型トランジスタの代替技術として、最先端のFinFETやFD-SOI(完全空乏型シリコン・オン・インシュレーター)の開発を進めている。また、RFやASICで利用されている、IBMで開発された既存プロセスも並行して促進している。

一方のTSMCは、自動車など特定の分野の顧客向けにカスタマイズしたプロセスを開発する取り組みを拡大している。

Patton氏は「多くの顧客が価値のある代替案を探している。チップの80%は最先端のものではない」と述べた。

IMECのSteegen氏は「チップの用途も広がっており、それが研究開発を促進する要素になっている」と語る。

IMECは、システムと半導体プロセスを共同で設計する時代が到来すると述べている。

Steegen氏によると、半導体ロードマップは従来、さらなる小型化を目指す“ボトムアップ型”の競争だったが、「現在ではシステムやアプリとの関連性がより高まりつつある」という。さらに同氏は「用途分野が非常に多岐にわたる上に、どの企業も独自の製品を欲しがるため、プロセス技術のカスタマイズは今後さらに進むだろう」と述べた。

⇒「「ITF 2016」で語られた半導体の未来」連載バックナンバー

【翻訳:青山麻由子、編集:EE Times Japan】

関連記事

「ムーアの法則」を超えた進化

「ムーアの法則」を超えた進化

Intelをはじめとした半導体メーカーは「ムーアの法則」に従うように、ほぼ2年に1度のペースで新たな微細プロセステクノロジーを導入し進化を続けてきた。しかし、近年は少しその様子が変わりつつある。特に台頭著しい新興メーカーは、独自のペースで進化を遂げてきている。 ARM、TSMCと7nm FinFET開発で協業

ARM、TSMCと7nm FinFET開発で協業

ARMとTSMCが、データセンサーやネットワークインフラ向けに、7nm FinFET開発で協業する。サーバ市場での勢力拡大に積極的なARMは、7nmプロセスの採用によるチップの高性能化を非常に重要視していると専門家は話す。 Intel、10nmプロセスでは新技術は導入せず

Intel、10nmプロセスでは新技術は導入せず

Intelは「ISSCC 2016」でムーアの法則の維持と“ポストCMOS”について講演し、10nmプロセスでは新しい技術は導入しないことを断言した。 5000円 中国格安スマートウォッチの伸びしろ

5000円 中国格安スマートウォッチの伸びしろ

今回は、中国で5000円以下で売られていたiaiwaiのスマートウォッチ「C600」を解剖していく。ほとんど日本では知られていない製品だがGSM対応の通信機能などを持つ。分解してみると意外にも将来を見据えた設計となっていたのだった――

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR