NVIDIAが高性能コンピュータの回路技術を解説:福田昭のデバイス通信(96) 高性能コンピューティングの相互接続技術(1)(2/2 ページ)

» 2017年01月11日 11時30分 公開

[福田昭,EE Times Japan]

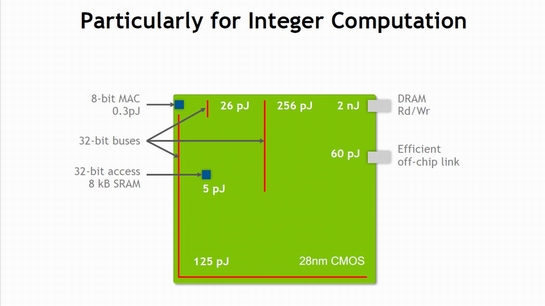

同じSoCで、処理を整数演算に限定して消費エネルギーを見積もってみよう。演算ユニットのエネルギーは劇的に低下するものの、相互接続(バスとリンク)が消費するエネルギーはある程度の低下にとどまるか、まったく減らない場合すらある。

例えば演算ユニットは8ビットの積和演算器となるので、消費エネルギーは0.3pJと倍精度浮動小数点演算器に比べて70分の1近くにまで減少する。ところがバスは32ビット・バスとバス幅が狭くなるものの、長さの短いバスにおける消費エネルギーは26pJと変わらない。また、長いバスと外付けDRAMのリンクが消費するエネルギーは8分の1に下がる。これも演算器の70分の1に比べると、低減の度合いは大きくない。

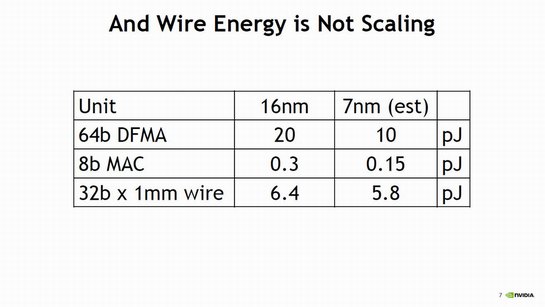

相互接続の消費エネルギーはスケーリングしない

もう1つの重要な課題に、相互接続はスケーリングしないという事実がある。例えば16nm技術と7nm技術を比べると、演算器の消費エネルギーはほぼ半分に減る。ところが、32ビット幅で長さが1mmのバス配線だと、消費エネルギーはわずか1割ほどしか減らない。消費エネルギー全体に占める相互接続部分の割合は、微細化によって増加していくことが分かる。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

IEDMで発表されていた3D XPointの基本技術(前編)

IEDMで発表されていた3D XPointの基本技術(前編)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。 ルネサス、フィン構造のMONOSフラッシュを開発

ルネサス、フィン構造のMONOSフラッシュを開発

ルネサス エレクトロニクスが、フィン構造を採用したSG(Split-Gate型)-MONOSフラッシュメモリセルの開発に成功したと発表した。フィン構造としたことで、FinFETなど先端のロジックプロセスとの親和性が高くなり、次世代の16nm/14nm世代マイコンに混載できるようになる。 SanDiskが語る、半導体不揮発性メモリの開発史

SanDiskが語る、半導体不揮発性メモリの開発史

今回からは、国際学会で語られたSanDiskの抵抗変化メモリ(ReRAM)の研究開発動向について紹介していく。まずは、約60年に及ぶ「不揮発性メモリの歴史」を振り返る。 Intel、IoTを巡ってARMと対決

Intel、IoTを巡ってARMと対決

Intelがこのほど、自動車、産業機器市場向けのリアルタイム性能を備えた新SoCを発表したことで、ARMとのIoT(モノのインターネット)の市場を巡る戦いが激化しつつある。 スピン注入型MRAMの不都合な真実

スピン注入型MRAMの不都合な真実

STT-MRAMの基礎を解説するシリーズ。最終回となる今回は、磁気トンネル接合(MTJ)を構成する固定層や磁性層に焦点を当てる。スピン注入型MRAMのMTJは、47層もの層で構成されている。これほどの層が必要なのにはきちんとした理由があるのだが、実は同時にそれがSTT-MRAMの弱点にもなっている。 半導体業界の秩序を変えた「チップセットの支配力」

半導体業界の秩序を変えた「チップセットの支配力」

今回は、半導体業界とその周辺にこの10年で最も大きな変化をもたらした要因である「チップセット」を取り上げる。チップセットの勃興を振り返りつつ、国内半導体メーカーがなぜチップセット化の流れに乗り遅れたのか、私見を述べたい。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

Special SitePR

あなたにおすすめの記事PR