AIへの熱視線続く、推論エンジンの需要が高まる見込み:半導体メーカーの競争も激化か(2/2 ページ)

Googleの「TPU」

機械学習(マシンラーニング)チップにおける革新的技術を切望する業界にとって、ターニングポイントとなったのが、Googleが2016年5月に発表した人工知能(AI)向けアクセラレーターチップ「Tensor Processing Unit(TPU)」だ。Googleは、「TPUは、商用FPGAやGPUよりも1桁高いワット当たり性能を実現する」と説明している。Googleは、このTPUが、同社のAI「AlphaGo(アルファ碁)」に使われていることを明かしている。ただしGoogleは、TPUのアーキテクチャの詳細には言及しておらず、TPUを販売する予定もないようだ。

多くのSoC設計者は、Googleの動きを見て、機械学習向けにはカスタムのアーキテクチャが欠かせないと思ったようだ。だが、より重要なのは、ディープニューラルネットワークの性能の指標となるものが、現時点では業界にはないという点である。

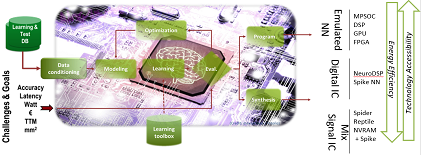

CEA-Letiは、「推論エンジン向けのさまざまなハードウェアアーキテクチャを調べるツールの準備は整っている」と述べている。同機関は、設計者がディープニューラルネットワーク構造を生成、調査できる「N2D2」というソフトウェアフレームワークを開発したという。Duranton氏は、「われわれは、ディープニューラルネットワークに適したハードウェアを選択するツールとしてN2D2を開発した。N2D2は、2017年第1四半期にオープンソースとしてリリースする予定だ」と述べている。

この新ツールの鍵となるのは、認識精度に基づく比較だけではなく、処理時間やハードウェアのコスト、エネルギー消費の観点からもハードウェアを比較できる点だ。Duranton氏は、「ディープラーニング向けのアプリケーションは、ハードウェア実装ごとに異なるパラメーターが必要になると考えられるため、こうした機能が極めて重要となる」と説明している。

N2D2は、マルチコア/メニーコアのCPUやGPU、FPGAを含む既成の商用ハードウェア向けのベンチマーク機能も搭載しているという。

CEA-Letiは、エッジコンピューティングにディープニューラルネットワークを導入する方法を研究してきた。Duranton氏は、「エッジコンピューティングにディープニューラルネットワークを導入する際の障壁は何か?」という質問に対し、「浮動小数点型サーバソリューションは消費電力、サイズ、レイテンシなどの制約があるため適用できない。その他にも、バンド幅やオンチップメモリ容量などの制約がある」と答えた。

Duranton氏は、専用アーキテクチャでは、スパイクコーディングのような新しいコーディング技術が使用されるとみている。

CEA-Letiの研究者は、ニューラルネットワークの特性を研究する中で、ニューラルネットワークは本質的に、コンピューティングエラー(計算誤差)に寛容であることを発見した。この発見によって、ニューラルネットワークは「近似計算」に対する適正があることが分かった。

そうだとすれば、必ずしもバイナリコーディングが必要なわけではないかもしれない。スパイクコーディングのようなテンポラルコーディングは、エッジノードでエネルギー効率がより一層優れていることを考えると、これは朗報といえる。

スパイクコーディングの利点は、スパイクコード化された(もしくはイベントベースの)システムでニューラルシステム内のデータがどのように符号化されるかが分かることだ。さらに、イベントベースのコーディングは、専用センサーや前処理と互換性を持たせることも可能だ。

神経システムで使われるものに近いコーディングであれば、ミックスドアナログやデジタル実装が簡単になり、エネルギー消費の小さい小型ハードウェアを構築できるというメリットもある。

【翻訳:滝本麻貴、編集:EE Times Japan】

関連記事

GoogleからAI用プロセッサ「TPU」が登場

GoogleからAI用プロセッサ「TPU」が登場

Googleが、人工知能(AI)に向けたアクセラレータチップ「Tensor Processing Unit(TPU)」を独自開発したことを明らかにした。同社が2015年にリリースした、オープンソースのアルゴリズム「TensorFlow」に対応するという。 我々が求めるAIとは、碁を打ち、猫の写真を探すものではない

我々が求めるAIとは、碁を打ち、猫の写真を探すものではない

ちまたには「人工知能」という言葉が氾濫しています。ですが、明言しましょう。「人工知能」という技術は存在しません。そして、私たちがイメージする通りの「人工知能」の実現も、恐らくはまだまだ先になるでしょう。 ディープラーニングの学習で「世界最高速度」実現

ディープラーニングの学習で「世界最高速度」実現

富士通研究所は2016年8月9日、スーパーコンピュータのソフトウェア並列化技術を応用し、複数のGPUを用いてディープラーニングの学習速度を高速化するソフトウェア技術を開発したと発表した。 沈黙する人工知能 〜なぜAIは米大統領選の予測に使われなかったのか

沈黙する人工知能 〜なぜAIは米大統領選の予測に使われなかったのか

世界中が固唾をのんで、その行方を見守った、2016年11月8日の米国大統領選挙。私は、大統領選の予測こそ、人工知能(AI)を使い倒し、その性能をアピールする絶好の機会だとみていたのですが、果たしてAIを手掛けるメーカーや研究所は沈黙を決め込んだままでした。なぜか――。クリントンvsトランプの大統領選の投票を1兆回、シミュレーションしてみた結果、その答えが見えてきました。 組み込み機器側に学習機能を搭載、高精度に推論

組み込み機器側に学習機能を搭載、高精度に推論

三菱電機は、組み込み機器に実装できる「ディープラーニングの高速学習アルゴリズム」を開発した。「コンパクトな人工知能」と組み合わせることで、車載機器や産業用ロボット側に学習機能を搭載することができ、より高精度の推論を行うことが可能となる。 AIの“苦悩”――どこまで人間の脳に近づけるのか

AIの“苦悩”――どこまで人間の脳に近づけるのか

人工知能(AI)の研究が始まった1950年代から、AI研究の目的は「人間の大脳における活動をいかにコンピュータ上で実現させるか」だ。大手IT企業や大学の努力によって、AIは少しずつ人間の脳に近づいているのは確かだろう。一方で、自然言語処理の分野では、“人間らしさ”を全面に押し出した「人工無能(人工無脳)」も登場している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- デンソー、ロームに対する株式取得提案を正式表明

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

CEA-Letiが開発した「N2D2」 出典:CEA-Leti

CEA-Letiが開発した「N2D2」 出典:CEA-Leti