NVIDIAがMOSFETの比例縮小則(デナード則)を解説(前編):福田昭のデバイス通信(97) 高性能コンピューティングの相互接続技術(2)(2/2 ページ)

デナード・スケーリングの終わり

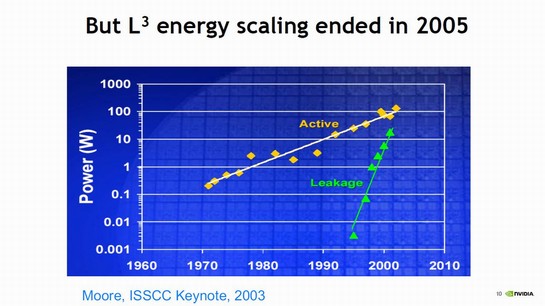

しかし、「魔法」は永遠には続かない。1990年代後半から、微細化とともにMOSFETのリーク電流が急激に増加し始める。もともと、消費電力はデナード・スケーリング通りとはいかず、動作時の消費電力は微細化の世代ごとに増え続けていた。ただし、CMOSデバイスでは、待機時の消費電力は無視できるほどに小さかった。ところが、MOSFETの性能を決めるもう1つの重要な指標である、「電圧入力と電流出力の比率(トランスコンダクタンス)の確保」という制約が、リーク電流(オフ電流)の増加という問題を無視できないものへと押し上げた。

半導体集積回路では、前段のMOSFETのドレイン電流が、次段のMOSFETのゲート容量を充電するために必要な時間が、回路の遅延時間(速度)を大きく左右する。前段のMOSFETの電圧入力の変化によって、ドレイン電流がどのくらいに変化するかを示した指標がトランスコンダクタンス(gm)である。当然ながら、トランスコンダクタンスは高いことが望ましい。

トランスコンダクタンス(gm)はゲート電圧としきい電圧の差分に依存しており、この差分が大きいほど、gmが大きくなる。また飽和ドレイン電流は、ゲート電圧としきい電圧の差分の2乗に比例する。

しきい電圧は微細化してもあまり変わらない(厳密には短チャンネル効果を防ぐことでしきい電圧の低下が生じないようにしている)。すると、微細化とともに電源電圧を下げると、ゲート電圧としきい電圧の差分が小さくなり、gmが下がり、ドレイン電流が下がる。すると回路の動作速度が上がらなくなる。

微細化によるドレイン電流の低下を防ぐ手段の1つは、しきい電圧を下げることだ。するとオフ状態の電流(サブスレッショルドリーク電流)が増える。つまり、待機時の消費電力が増大する。リーク電流を増やさないためには、しきい電圧を下げずに、一定のままにしておきたい。すると電源電圧を下げられない。ドレイン電流を確保するためにだ。この場合は、微細化しても動作時の消費電力が大幅に増えてしまう。「デナード・スケーリングの終わり」である。

2000年代の半ばには、古典的なデナード・スケーリングは破綻する。そして修正版のデナード・スケーリング(ポスト・デナード・スケーリング)が登場する。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

「ムーアの法則」を超えた進化

「ムーアの法則」を超えた進化

Intelをはじめとした半導体メーカーは「ムーアの法則」に従うように、ほぼ2年に1度のペースで新たな微細プロセステクノロジーを導入し進化を続けてきた。しかし、近年は少しその様子が変わりつつある。特に台頭著しい新興メーカーは、独自のペースで進化を遂げてきている。 IoT端末に最適? Apple Watch Series 2の心臓部「S2」に迫る

IoT端末に最適? Apple Watch Series 2の心臓部「S2」に迫る

2016年9月に発売されたAppleの腕時計型ウェアラブル端末「Apple Watch Series 2」を取り上げる。中身の大転換が図られたiPhone 7同様、配線経路の大幅な見直しが行われた他、心臓部の「S2」でも新たな工夫が見受けられた。 「SEMICON West 2016」、imecが展望する5nm世代の配線技術(前編)

「SEMICON West 2016」、imecが展望する5nm世代の配線技術(前編)

imceによる、5nm世代のロジック配線プロセスを展望した講演を、前後編の2回にわたりお届けする。前半では、配線抵抗(R)、配線容量(C)、RC積という配線のパラメータの特徴を紹介する。さらに、10nm世代、7nm世代、5nm世代と微細化が進むと、配線抵抗(R)、配線容量(C)、RC積がどのように変化していくかを解説する。 STT-MRAMの基礎――情報の蓄積に磁気を使う

STT-MRAMの基礎――情報の蓄積に磁気を使う

次世代不揮発メモリの候補の1つに、STT-MRAM(スピン注入磁化反転型磁気メモリ)がある。データの読み書きが高速で、書き換え可能回数も多い。今回から始まるシリーズでは、STT-MRAMの基本動作やSTT-MRAが求められている理由を、「IEDM2015」の講演内容に沿って説明していこう。 EUVは、微細化の“万能策”ではない

EUVは、微細化の“万能策”ではない

半導体製造プロセスの微細化を進めるには、EUV(極端紫外線)リソグラフィーが鍵になるといわれている。ばく大な資金が、同技術の開発に投入されているが、その進捗は必ずしも期待通り、予定通りではないようだ。 わずかな微細化、見合わぬ労力

わずかな微細化、見合わぬ労力

「IMEC Technology Forum(ITF) 2016」では、半導体業界の将来に関する基調講演やインタビューが多数行われた。GLOBALFOUNDRIESのCTOを務めるGary Patton氏は、「2年ごとにコストを35%ずつ下げ、性能を20%ずつ上げることのできた時代は20nmプロセスで終わった」と述べる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増