NVIDIAがMOSFETの比例縮小則(デナード則)を解説(後編):福田昭のデバイス通信(98) 高性能コンピューティングの相互接続技術(3)

後編では、修正版のデナード・スケーリングを解説する。修正版のデナード・スケーリングでは、微細化によってMOSFETの密度は2倍に増えるものの、動作速度は高くならず、消費電力は1.4倍となる。そのため、消費電力を増やさないためには、MOSFETの密度を2倍ではなく、1.4倍にとどめる必要があるのだ。

修正版のデナード・スケーリングとは

2016年12月に開催された国際学会IEDMのショートコースから、「将来のコンピュータにおける相互接続の課題(Interconnect Challenges for Future Computing)」と題するNVIDIAの講演概要をご紹介している。講演者はNVIDIAで研究担当シニア・バイスプレジデント兼チーフサイエンティストを務めるWilliam(Bill) Dally氏である。

シリーズの第2回である前回は、MOSFETの微細化をけん引してきた古典的な「デナード・スケーリング(比例縮小則)」を説明した。今回は、修正版のデナード・スケーリングを解説する。

なお講演だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Dally氏の講演内容を適宜、補足している。あらかじめご了承されたい。

前回で説明したように、「デナード・スケーリング(古典的なデナード・スケーリング)」は、高速化の維持と消費電力の増大のトレードオフ関係によって2000年代半ばに終えんを迎える。代わって「修正版のデナード・スケーリング(ポスト・デナード・スケーリング)」が、MOSFETを微細化するときの現実に近い法則となる。

微細化してもトランジスタが速くならない

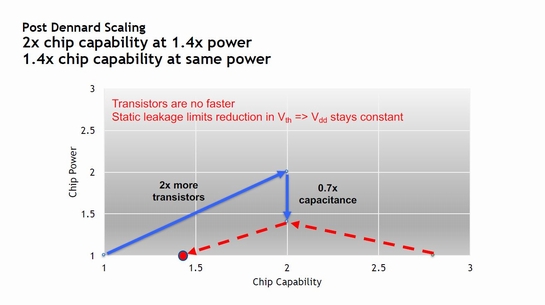

修正版のデナード・スケーリングでは、微細化によってMOSFETの密度は2倍に増えるものの、動作速度は高くならない。消費電力はどうなるか。微細化によってMOSFETのゲート容量は減少する。容量の減少によって消費電力は下がる。ただし、リーク電流抑制と性能維持のトレードオフによって電源電圧は下げられない。

従って古典的なデナード・スケーリングとは違い、消費電力は1.4倍に増える。消費電力を増やさずに済むためには、MOSFETの密度を2倍ではなく、1.4倍にとどめる必要がある。

「修正版のデナード・スケーリング(Post Dennard Scaling)」。横軸はチップの能力、縦軸はチップの消費電力(いずれも単位面積当たり)。修正版のデナード・スケーリングでは、MOSFETの密度は2倍に増えるものの、動作速度が向上しない。出典:NVIDIA(クリックで拡大)

「修正版のデナード・スケーリング(Post Dennard Scaling)」。横軸はチップの能力、縦軸はチップの消費電力(いずれも単位面積当たり)。修正版のデナード・スケーリングでは、MOSFETの密度は2倍に増えるものの、動作速度が向上しない。出典:NVIDIA(クリックで拡大)微細化するとともに微細化の恩恵が減少

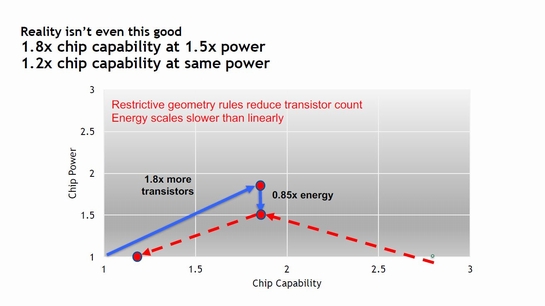

悲しいことに最先端の製造技術では、微細化による恩恵は修正版のデナード・スケーリングよりも少なくなっている。Dally氏が説明した現実の比例縮小は、トランジスタのレイアウトの制約によってトランジスタ数の増加は1.8倍にとどまり、消費電力は1.4倍ではなく、1.5倍に増えるというものだ。消費電力を微細化前と同じ値に維持するためには、トランジスタ数の増加は1.2倍にとどめなければならない。

(次回に続く)

関連記事

中国のメモリ市場、2017年はどう動くのか(前編)

中国のメモリ市場、2017年はどう動くのか(前編)

半導体産業の拡大と強化に国をあげて注力する中国。その中国が現在、焦点を当てているのがメモリ分野だ。 進む7nmプロセスの開発、TSMCとIBMが成果を発表

進む7nmプロセスの開発、TSMCとIBMが成果を発表

米サンフランシスコで開催された「IEDM 2016」では、TSMCとIBMがそれぞれ最新プロセス技術について発表し、会場を大いに沸かせたようだ。 微細化とIoTと2つの潮流に対応した装置、SCREEN

微細化とIoTと2つの潮流に対応した装置、SCREEN

SCREENセミコンダクターソリューションズは、「SEMICON Japan 2016」で、「微細化」と「IoT」という、半導体市場における2つの大きなトレンドに対応した製造装置をパネル展示した。 7nmプロセス開発、ファウンドリー間の競争激化

7nmプロセス開発、ファウンドリー間の競争激化

2016年12月に米国で開催される、最先端電子デバイスの研究開発に関する国際学会「IEDM 2016」で、TSMCが7nmプロセスに関する発表を行う。7nmプロセスの研究開発では、TSMC、GLOBALFOUNDRIES(GF)、Samsung Electronics(サムスン電子)が火花を散らしている。 EUVは、微細化の“万能策”ではない

EUVは、微細化の“万能策”ではない

半導体製造プロセスの微細化を進めるには、EUV(極端紫外線)リソグラフィーが鍵になるといわれている。ばく大な資金が、同技術の開発に投入されているが、その進捗は必ずしも期待通り、予定通りではないようだ。 微細化、「3nmまでいくのでは」

微細化、「3nmまでいくのでは」

「ムーアの法則」の生みの親であるGordon Moore氏が、ハワイの自宅でベルギーIMECのビデオインタビューに応じ、未来の技術に関する自身の見解や、1965年以来半導体業界に大きな影響を及ぼし続けてきたムーアの法則の今後について語った。87歳となった同氏は、謙虚なエンジニアはいつまでも自分を笑いの種として語れることを示してみせた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼