EE Times Japan >

プロセス技術 >

シリコンインターポーザを導入した高性能パッケージの製品例:福田昭のデバイス通信(108) TSMCが解説する最先端パッケージング技術(7)(2/2 ページ)

» 2017年05月08日 11時30分 公開

[福田昭,EE Times Japan]

ロジックダイと高速DRAMモジュール「HBM」を集積

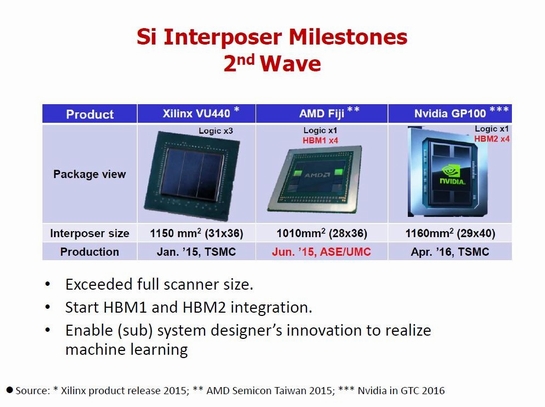

2015年〜2016年の第2期では、ロジックダイと高速DRAMモジュール「HBM1」および「HBM2」をシリコンインターポーザ上に集積したパッケージが登場するとともに、シリコンインターポーザのサイズが巨大化した。

FPGA最大手のXilinxは、20nm世代のFPGA「Virtex UltraScale」シリーズでハイエンド品の「XCVU440」にシリコンインターポーザ技術を導入した。3枚のロジックダイを集積している。シリコンインターポーザのサイズは31mm×36mm、面積は1150mm2である。「Virtex-7」シリーズの「2000T」ではサイズが25mm×31mm、面積が775mm2だったので、面積は約1.5倍に増えていることが分かる。

GPUベンダーのAMDは、大規模GPU「Fiji」にシリコンインターポーザ技術を採用した。GPUチップを1個と、「HBM1」モジュールを4個、シリコンインターポーザに載せている。AMDが2015年に展示会兼講演会「Semicon Taiwan」で発表した資料によると、プリント基板の実装占有面積を約3分の1に縮小できたとする。シリコンインターポーザの面積は1100mm2と大きい。

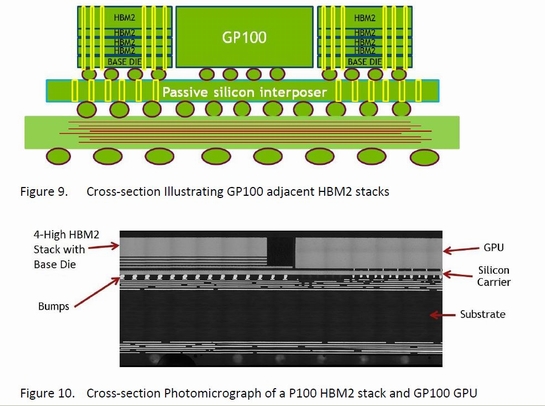

同じくGPUベンダーのNVIDIAは、大規模GPU「GP100」のパッケージにシリコンインターポーザ技術を採用した。GPUチップ「GP100」を1個と、「HBM2」モジュールを4個、シリコンインターポーザに載せている。シリコンインターポーザの面積は1160mm2とこれも巨大である。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

基材や形状を選ばない非真空ドライめっき技術

基材や形状を選ばない非真空ドライめっき技術

ベンチャー企業のFLOSFIAは、京都大学が開発した薄膜形成技術「ミストCVD法」を発展させ、基材の種類や形状に関係なく金属薄膜を成膜できる非真空ドライめっき技術「ミストドライ めっき法」を開発した。10μm以下の表面形状にも成膜可能で、半導体素子などの電極への応用が見込まれる。 ASML、2018年にEUV装置を20台以上出荷予定

ASML、2018年にEUV装置を20台以上出荷予定

ASMLは、2018年にEUV(極端紫外線)リソグラフィ装置を20〜24台出荷する計画だという。何度も延期を重ねながら開発を進め、ようやく出荷のメドが立ったようだ。 GFが中国に工場建設、痛手を負うのは?

GFが中国に工場建設、痛手を負うのは?

GLOBALFOUNDRIES(GF)が中国の成都に工場を建設する。巨額の資金を投じて半導体産業の強化を進める中国にとって、これは朗報だろう。では、痛手を被る可能性があるのは誰なのか。 TSMCが7nmなど最新プロセスの開発状況を報告(前編)

TSMCが7nmなど最新プロセスの開発状況を報告(前編)

TSMCは2017年3月15日(米国時間)にカリフォルニア州で開催したイベント「TSMC Technology Symposium」で、最先端プロセスの開発状況を報告した。その発表からは、FD-SOIプロセスへの対抗心が垣間見えた。 TSMC、10nmプロセスではインテルとの技術差なくなる

TSMC、10nmプロセスではインテルとの技術差なくなる

TSMCは、10nmプロセスを適用したチップの製造を2017年に開始する。同社は「インテルの10nmチップと同等レベルの性能を実現できると見ている。10nmプロセスで、インテルとの技術的なギャップを埋められるだろう」と述べている。 SanDiskが語る、抵抗変化メモリのセルアレイとセルの選択

SanDiskが語る、抵抗変化メモリのセルアレイとセルの選択

今回は、半導体メモリのメモリセルアレイと、アレイから特定のメモリセルを選択する手段について説明する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

Special SitePR

あなたにおすすめの記事PR