NANDフラッシュ、開発の視点はチップからソフトへ:Flash Memory Summit 2017(2/2 ページ)

フラッシュストレージシステム向けソフトは効率化が必要

ほぼ全ての大手ベンダーが、自社データセンターのレイテンシ(遅延時間)を減らすため、フラッシュストレージシステム向けのソフトウェアを効率化する必要があると主張した。

イベントに参加していたeBayのITマネジャーによると、フラッシュストレージを採用する上での最大の問題は、「Open Stack」や「Kubernetes」など、データセンターのタスクスケジューラーとして用いるオープンソースのプログラムに関連したものだという。現時点では、そうしたプログラムは、複数のアプリケーションにわたるHDDやフラッシュストレージのプールを共有する形で調整されていない。

eBayの主席ストレージアーキテクトであるManoj Wadekar氏は、「優れたデバイスは既にある。次に必要なのは、それを活用するためのインフラだ」と述べた。

一方、Webデータセンターでは、低コストのシングルポートのSSDを用いる傾向があるにもかかわらず、ベンダーはデュアルポートのSDDを強化している。Wadekar氏は「性能は、大容量のアプリケーションよりも急速に向上している」と述べた。

ストレージソフトウェアへの新しいアプローチ

Samsungは、ストレージソフトウェアへの全く新しいアプローチを提案している。それは、独立したブロックベースのシステムとファイルベースのシステムの間に以前から存在する違いをなくすものだという。このアプローチはいわゆる「キー・バリュー(key-value)型」であり、レイテンシの削減を実現するものだ。だが、そのために既存のアプリケーションを書き換えるには何年もかかる可能性があり、Samsungもそのことを認めている。

東芝のストレージ製品部門でゼネラルマネジャーを務めるSteve Fingerhut氏は、短いインタビューの中で、「既存のアプリケーションを書き換える試みは過去にも行われてきた。(中略)現在、世界は高性能のブロックベースのソフトウェアと、低性能のオブジェクトベースのソフトウェアに二分されている。将来的には1つに統合されるかもしれないが、数年はかかるだろう」と語った。

一方、Micronは、研究段階にあるソフトウェアについて発表した。このソフトウェアは、データセンターのフラッシュシステムの性能を大幅に高めながら、消費電力を低減するものだという。同社のSSDエンジニアリング部門でバイスプレジデントを務めるCurrie Munce氏は「このソフトウェアは将来的に、当社に実りをもたらす領域となる」と述べた。

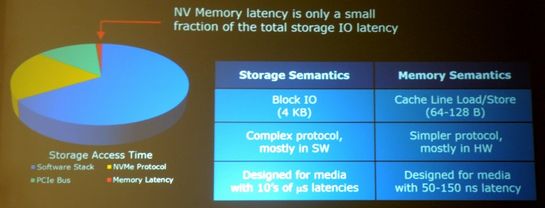

Western Digital(ウエスタンデジタル)のCTOであるMartin Fink氏によると、データセンターのフラッシュストレージで発生するレイテンシの大部分は、チップに起因するものではなく、システムレベルのソフトウェアの複雑なスタックによるものだという。同氏は「そのため、当社はより多くの時間をかけて、ハードウェアとソフトウェアの適切な組み合わせを見つけようとしている」と述べた。

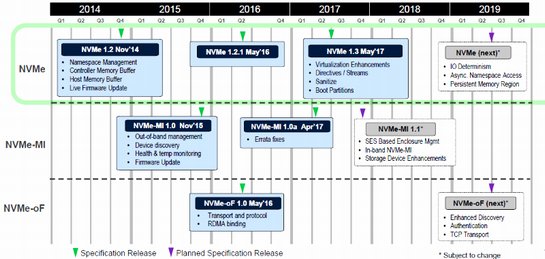

一方、次世代SSDの接続規格である「NVM Express(NVMe)」の策定団体は、PCI Express(PCIe)、Ethernet、Fibre Channelなどのインタフェース上で作動するプロトコルの新たな性能を発表した。新たなプレイヤーは、そのようなネットワークを簡素化するための新たな方法の発見に取り組んでいる。

新しいフォームファクタ

チップとソフトウェア以外では、データセンターにある小型のラックマウントシステムに、できるだけ多くのフラッシュメモリを搭載できるようにSSDを最適化しようとしている。

Samsungは、「M.3」のフォームファクタを披露した。外形寸法は30.5×110.0×4.38mmである。「M.2」よりも幅が広く、3D NANDフラッシュを使って最大16Tバイトまで搭載でき、5億IOPS(Input/Output Per Second)までサポートするという。

Intelは、1Uサイズの「Ruler」フォームファクタを公開した。PCIe 3だけでなく、今後2世代のPCIeまでサポートできるとしている。

【翻訳:青山麻由子、滝本麻貴、編集:EE Times Japan】

関連記事

PCIe SSDの性能を引き出す「NVMe」

PCIe SSDの性能を引き出す「NVMe」

今回はNVMe(Non-Volatile Memory Express)を紹介する。NVMeはストレージ向けのホスト・コントローラ・インタフェースの1つで、PCIe(PCI Express)インタフェースを備えた高速のSSDを対象にした規格仕様である。 万能コネクタ「U.2」の概要

万能コネクタ「U.2」の概要

今回は、SSDインタフェースのフォームファクタの中でも、最近注目を集めている「U.2(ユー・ドット・ツー)」と、「M.2(エム・ドット・ツー)」を紹介する。この2つは、しばしば混同されてきたが、明確に異なっている。 WD、東芝とのメモリ合弁事業に投資継続の意思を強調

WD、東芝とのメモリ合弁事業に投資継続の意思を強調

Western Digital(ウエスタンデジタル/WD)は2017年8月2日(米国時間)、東芝とのNAND型フラッシュメモリの合弁事業に対し、今後も投資を行うとの声明を発表した。この発表の直前に東芝は、東芝メモリのメモリ新製造棟(四日市工場)への投資について協議中だったSanDisk(サンディスク:WDの子会社)と合意に至らなかったため、東芝メモリ単体で投資を続行すると発表していた。 Micronの台湾DRAM工場が稼働停止、供給に影響か

Micronの台湾DRAM工場が稼働停止、供給に影響か

Micron Technologyの子会社であるInotera MemoriesのDRAM製造工場の稼働が停止したことで、DRAMの世界供給量が低下する可能性が出てきた。それにより、価格の上昇も懸念されている。 2017年Q2の半導体売上高、SamsungがIntelを抜く

2017年Q2の半導体売上高、SamsungがIntelを抜く

2017年第2四半期の半導体売上高において、Samsung ElectronicsがIntelを抜いた。メモリ市場が好調だったことが主な要因だ。 米半導体業界、ポスト・ムーアの技術を模索

米半導体業界、ポスト・ムーアの技術を模索

米国防高等研究計画局(DARPA)は、来たる「ムーアの法則」の終息に備え、“ポスト・ムーア時代”の技術の模索を本格化させている。材料、アーキテクチャ、設計の自動化の3つにターゲットを絞り、まずは2億米ドルを投資してプロジェクトを行う予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Intelの「Ruler」

Intelの「Ruler」