モノリシック3D IC、将来有望ながら課題は山積:実用化に近いデモもない?(2/2 ページ)

M3Dに似た技術の模索

CEA-Letiをはじめ、さまざまな企業が、M3Dを適用してロジックとメモリを接続した業界初となるシリコンの実用化の例として、ソニーのCMOSイメージセンサーを挙げている。ソニーは2017年1月に、Samsung Electronicsとの協業により、3層積層技術に関する論文を発表した。Samsungは最近、「将来的には、3D NAND型フラッシュメモリチップに周辺回路を集積する予定だ」と述べており、M3Dとよく似た手法を提案している。

CEA-Letiは現在、Cool Cube技術をさらに推進すべく、マルチプロジェクトウエハー(MPW)向けプロセス開発ツール(PDK:Process Development Kit)を手掛けているところだ。2018年後半には、パートナー企業が技術試験を実施できるようになる込みだという。また、「Chip on Wafer(CoW)」や「Wafer on Wafer(WoW)」などの積層技術についても、一部取り組みを進めているという。

CEA-Letiは、2×107vias/mm2を積層するCool Cube技術を披露した。また、温度の問題への対応や、正確な配列を実現するCool Cube構造について、その取り組みの成果を発表した。CEA-Letiのセクションマネジャーを務めるOlivier Faynot氏は、「われわれとしては、Cool Cube技術を適用した製造は可能だと確信している」と述べている。

Or-Bach氏は、既存の製造技術を組み合わせることにより、少なくとも4つのデバイスを比較的低コストで積層することが可能だとするアイデアを披露している。同氏は、SiGe(シリコンゲルマニウム)のガイドレイヤーを使用して、研削加工でコンポーネントを切り離し、向かい合わせて固定するという手法について発表した。SiGeガイドレイヤーは、後からエッチング除去されるという。

Or-Bach氏の手法の要素の1つとなっているのが、許容誤差50nm未満での配列が可能な既存のボンダーである。同氏は、「1つのダイ上にメモリと周辺回路を集積するDRAMを構築する際に、私が発表したコンセプトを適用することができるだろう」と提案している。

Qualcomm ResearchのシニアディレクターであるYang Du氏は、「M3Dは、幅広い種類の製品に適用することが可能だ。メモリアレイと複数の積層ユニットアレイとを組み合わせることにより、理想的なニューラルネットワークアクセラレーターを実現することができる」と述べ、イベントの他の登壇者たちとの間でその適用例を共有した。

いかに多くのEDAベンダーを引き込めるか

短期的に最大の障壁の1つとなっているのが、いかに多くのEDAベンダーを取り組みに参加させるかという点だ。Mentor Graphicsの代表者が、M3D構造の寄生素子抽出と検証に関する初期段階の取り組みについて説明している。QualcommとARMは、M3D設計ツールの開発において、ジョージア工科大学(Georgia Institute of Technology)などの大学と協業しているという。

ARM Researchの代表者であるMudit Bhargava氏は、「この先、まだ道のりは長い。今のところ、非常に有望な微粒子3D技術を確立することはできたが、難しい課題は数多く残っている」と述べている。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

3次元集積化(3D IC)の理想と現実

3次元集積化(3D IC)の理想と現実

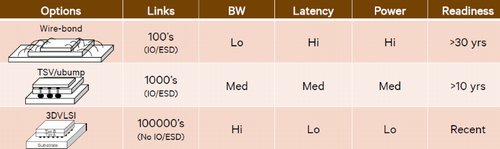

今回は、なぜシステムを複数のチップに分ける必要があるのかを説明する。後半では、パッケージに求められる目標を達成する“究極のパッケージング技術”として期待されたシリコン貫通ビア(TSV: Through Silicon Via)と、旧世代のパッケージング技術との間に存在する、大きなギャップについて解説したい。 3Dチップ技術、データセンターへの活用を視野に

3Dチップ技術、データセンターへの活用を視野に

マイクロプロセッサの研究プロジェクトを中止したOracle(オラクル)。Oracleの元主席エンジニアはスタートアップを立ち上げ、データセンサー向けのチップ積層技術の開発を続けている。 “メモリ大国”を目指す中国(前編)

“メモリ大国”を目指す中国(前編)

中国がメモリ技術の開発に注力している。中国のファウンドリーであるXMCは、「3D NAND型フラッシュメモリでSamsung Electronicsに追い付く」と、非常に積極的な姿勢を見せている。 TSMC、7nm/EUVの開発状況をアップデート

TSMC、7nm/EUVの開発状況をアップデート

TSMCは2017年9月、米国で開催されたイベントで7nmプロセス技術やEUV(極端紫外線)リソグラフィの開発状況などを説明した。 ニューラルプロセッサIP、AI搭載モバイルを後押し

ニューラルプロセッサIP、AI搭載モバイルを後押し

Imagination Technologies(イマジネーションテクノロジーズ)が、ニューラルネットワークの処理に特化したアクセラレーター「PowerVR 2NX NNA」を発表した。モバイル機器にAI(人工知能)を搭載する動きが進む中、「今後のキーテクノロジーになる」と同社は語る。 「半導体の可能性を強く信じる」 AppleのCOO

「半導体の可能性を強く信じる」 AppleのCOO

TSMCの創立30周年記念式典で、Apple COO(最高執行責任者)であるJeff Williams氏が、TSMCとのパートナーシップや、半導体業界の今後の10年などについて語った。同氏は、半導体の可能性を強く信じていると強調した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

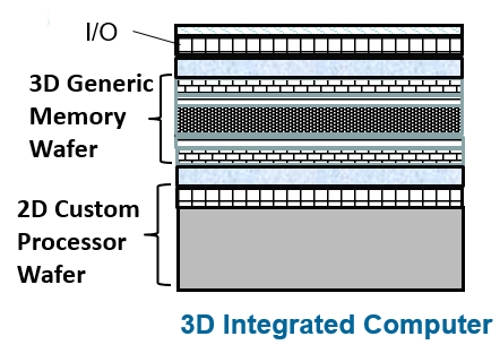

Zvi Or-Back氏は、同氏が提案するM3D技術の概要を教えてくれた 出典:MonolithIC 3D

Zvi Or-Back氏は、同氏が提案するM3D技術の概要を教えてくれた 出典:MonolithIC 3D