Cypressの「HyperBus」、xSPI規格に採用:8ビットシリアルメモリI/F

Cypress Semiconductorのメモリインタフェース規格「HyperBus」が、JEDECが策定する新しい「eXpanded SPI(xSPI)」インタフェース規格に採用された。

Cypressの「HyperBus」がJEDECで標準化へ

Cypress Semiconductor(以下、Cypress)は、これまで数年間にわたり広く採用されてきた同社の「HyperBus」(8ビットシリアルメモリインタフェース)が、標準化される予定であることを発表した。同社にとっては短期的にみて、大きな強みとなるだろう。また長期的には、標準ベースの代替規格の策定が促進されていくとみられる。

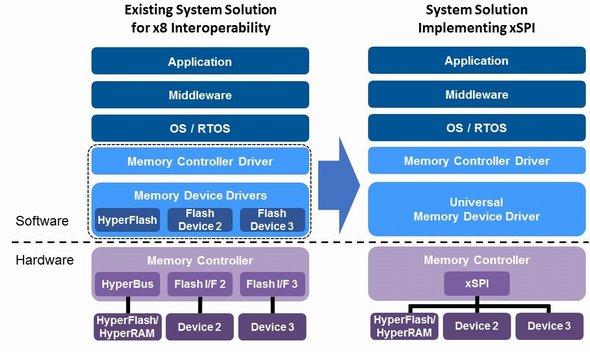

Cypressは、「当社の高帯域幅向けHyperBusが、米国の電子部品関連標準化団体『JEDEC Solid State Technology Association』の新しい電気的インタフェース規格『eXpanded SPI(xSPI)』に採用される予定だ」と述べている。xSPI標準規格は、高性能x8シリアルインタフェースの互換性に関する要件として、読み出し/書き込みコマンドや電気特性、コマンドおよびデータ伝送速度用の信号プロトコルの他、BGA設置面積の標準ピン配列などを定義する。JEDECの担当者は、「この件に関しては、まだ最終決定されていないため、コメントできない」としている。

Cypressのフラッシュ事業部門担当バイスプレジデントを務めるRainer Hoehler氏は、EE Timesの電話インタビューの中で、「HyperBusインタフェースがJEDECのxSPI標準規格に採用されることにより、HyperBusベースのメモリ設計を簡素化できるだけでなく、自動車、産業、IoT(モノのインターネット)用途向けのインスタント起動機能を、もっと柔軟に実装できるようになるだろう。HyperBusは、起動時間の高速化や、XIP(Execute-In-Place)をフラッシュメモリから直接実行することができる他、必要なRAMの数を削減することも可能だ」と述べている。

12ピンのHyperBusは、8ピンのアドレス/データバスと、差動クロック(2信号)、チップセレクト1個、コントローラー向けRDS(Read Data Strobe)で構成されている。自動車用計器群や、インフォテインメントおよびナビゲーションシステム、ファクトリーオートメーション(FA)など、幅広い種類の高性能アプリケーションを実現することが可能だ。

Hoehler氏は、「HyperBusの標準化により、エコシステム構築に向けた道が開かれるだけでなく、異なる種類のxSPI技術を集められるようになるため、開発者たちは、自社システムでどのメモリデバイスを使うのかを選択することが可能だ。チップセットメーカーやその顧客企業にとっては、利便性が大きく向上するだろう」と述べる。

同氏は、「Cypressは、自動車市場において数多くのデザインウィンを獲得しているので、HyperBusを適用するのは問題ないだろう。だが産業市場は現在、断片化が進んでおり、それぞれ選択することが可能な標準規格に対して、完全に依存しているという状況にある」と述べる。

Cypressは、自動車と産業という上記2つの市場の他にも、HyperFlashにはネットワーク機器分野において、5G(第5世代移動通信)技術をサポートするというチャンスがあるとみているようだ。

同社は、「利益率の低いコモディティ製品事業への注力を減らし、IoTや自動車、USB Type-Cといった分野で成長できたことから、2017年第3四半期の業績は好調だった。当社は2016年、IoTに注力すべく、“Cypress 3.0”という戦略を掲げ、始動したが、予想を上回る速さで成果を上げることができた」と述べている。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

これから世界を席巻する!? USB Type-Cを知る

これから世界を席巻する!? USB Type-Cを知る

これから、世界を席巻するであろう新しいコネクタ『USB Type-C』(USB-C)。USB前夜や歴代USBコネクタを振り返りながら、素晴らしいUSB Type-Cを紹介していこう。 産業用IoT向けイーサネットは次世代へ

産業用IoT向けイーサネットは次世代へ

産業機器分野においてIoT(モノのインターネット)を普及させる手段の1つとして、「IEEE 802.1 TSN(Time Sensitive Networking)」と呼ばれる次世代規格の標準化が進んでいる。標準イーサネットの拡張版である同規格は、コストや相互運用性などの面でメリットを生み出す可能性がある。 VR、標準化への道のりはまだ遠く

VR、標準化への道のりはまだ遠く

スマートグラスの台頭とともに、VR(仮想現実)技術が著しく進化している。だがそれ故、標準化のスピードが追い付いていないようだ。 標準化進むセルラーIoT、モジュールは低価格に

標準化進むセルラーIoT、モジュールは低価格に

IoT(モノのインターネット)機器をモバイルネットワークに接続する「セルラーIoT」の標準化が進んでいる。エリクソン・ジャパンは2016年6月16日に横浜市で記者説明会を開催し、セルラーIoTの技術解説やデモを行った。 ウェアラブル脳波計は私たちの本音を伝えてくれる

ウェアラブル脳波計は私たちの本音を伝えてくれる

情報通信研究機構の成瀬康氏は、IEEEが開催した「ヒューマンインタフェースと脳科学」に関するセミナーで、日常での脳波計測を可能とするウェアラブル脳波計に関する研究成果を発表した。 Rambus、SemtechのIP事業を3250万ドルで買収へ

Rambus、SemtechのIP事業を3250万ドルで買収へ

Rambusが、SemtechのシリアルインタフェースIP(Intellectual Property)事業を買収する。Semtechは、アナログ/ミックスドシグナル製品に注力するとしていて、その戦略から外れる事業は手放す方針だった。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- デンソー、ロームに対する株式取得提案を正式表明

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- NVIDIAとメモリ3社、世界半導体売上高の42%占める