耐圧1200V級のオールSiCモジュールを可能に:新構造のSWITCH-MOSを開発

産業技術総合研究所(産総研)の研究グループらは、耐圧1200V級のショットキーバリアダイオード内蔵SiC(炭化ケイ素)トランジスターを開発し、量産試作品レベルでその性能や信頼性を実証した。【訂正】

HEVやEVの電力変換効率を大幅に改善

産業技術総合研究所(産総研)先進パワーエレクトロニクス研究センターSiCパワーデバイスチームの原田信介研究チーム長らによる研究グループは2017年12月、耐圧1200V級のショットキーバリアダイオード内蔵SiC(炭化ケイ素)トランジスターを開発し、量産試作品レベルでその性能や信頼性を実証したと発表した。この成果は富士電機との共同研究によるもので、ハイブリッド自動車(HEV)や電気自動車(EV)における電力変換システムのオールSiCモジュール化が可能となる。

SiCデバイスのみを用いたオールSiCモジュールは、シリコンデバイスを用いた場合に比べて、電力変換効率を大幅に改善できる。これに加えて、コスト低減や信頼性を向上させるためには、SBD(ショットキーバリアダイオード)内蔵型MOSFETを用いることが有効だといわれてきた。しかし、これまでは耐圧が3300V級以上のMOSFETでしか、高い信頼性は確認されていなかったという。

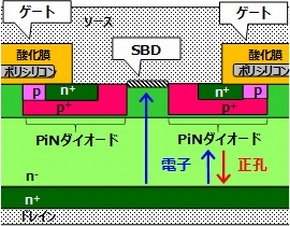

そこで研究グループは、トレンチ型MOSFETにトレンチSBDを内蔵する独自構造のデバイス「SWITCH-MOS(SBD-Wall Integrated Trench MOS)」を開発し、耐圧が1200V級のMOSFETでも、高い信頼性が得られることを実証した。

【訂正:2017年12月26日19時10分 上記図版の配置に誤りがあり、「一般的な構造」と「今回開発した構造」が左右反対に表示されていました。訂正してお詫び致します。】

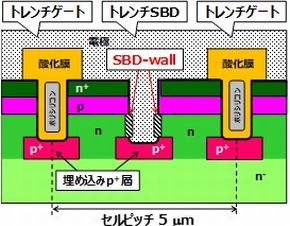

一般的なSBD内蔵MOSFETでは、SiC-MOSFETの内部にあるPiNダイオードが、SiC-SBDの代替として用いられる。しかし、SiCのPiNダイオードは、順方向に電圧を印加すると電流が低下する「順方向劣化」という現象が生じるため、信頼性に課題があったという。新開発のSBD内蔵MOSFETは、内部のPiNダイオードに印加する電圧(VPiN)が、ある値を超えないように抑えることで、PiNダイオードを不活性化するように工夫した。

研究グループは、VPiNがSBD部の電圧分担(VSBD)とP型領域周囲の電流広がり領域の電圧分担(V広がり)の和に等しいことに着目。耐圧保持領域となるドリフト層の電圧分担(Vドリフト)が小さい、1200V級のデバイスでもVPiNを抑えられるように、V広がりの低減を目指した。

開発したSWITCH-MOSは、セルピッチが狭くオン抵抗も小さいトレンチ型MOSFET「IE-UMOSFET」を基本構造としている。トレンチゲートの電界緩和層の埋め込みp+層上にトレンチを形成し、その側壁にSBD-wallを内蔵した構造である。この結果、SBDを内蔵しても5μmのセルピッチが保たれており、p型領域幅を最小限に抑えてV広がりを低減することができた。

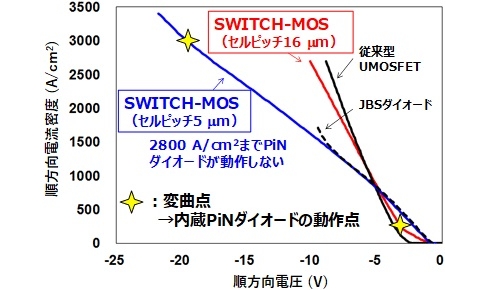

耐圧が1200V級のSWITCH-MOSは、セルピッチが16μmと広くなれば、約300A/cm2の電流密度でPiNダイオードが動作する。このため、SBDが内蔵されていない従来型UMOSFETとほぼ同じ電流−電圧特性を示すことになる。今回のようにセルピッチが5μmと狭くなればV広がりは抑制され、電流密度が2800A/cm2となっても、PiNダイオードの動作を不活性にすることができるという。

研究グループは、試作したデバイスを用いて順方向劣化試験も行った。試験後のフォトルミネッセンス像によると、従来型UMOSFETではPiNダイオードが動作して順方向劣化が生じ、積層欠陥が拡がっていることが分かる。これに対して、セルピッチが5μmのSWITCH-MOSは、積層欠陥の拡がりはなく、順方向劣化をしていないことが分かった。

研究グループは今後、事業化に向けた取り組みを強化する。デバイス構造多層化や製造プロセスの高度化を進めつつ、パッケージングなどの技術開発にも取り組む計画だ。

関連記事

産総研ら、電極表面の原子の動きを実時間で観察

産総研ら、電極表面の原子の動きを実時間で観察

産業技術総合研究所(産総研)らの研究グループは、燃料電池などのエネルギー変換に伴う原子の動きをリアルタイムに観察できる技術を開発した。 産総研ら、STOを用いた人工ニューロンを開発

産総研ら、STOを用いた人工ニューロンを開発

産業技術総合研究所(産総研)の常木澄人研究員らによる研究グループは、スピントルク発振素子(STO)を用いた人工ニューロンを開発した。これを用いたニューロモロフィック回路音声認識システムの音声認識正答率は99.6%と高い。 産総研、リチウムイオン電池充放電機構を解明

産総研、リチウムイオン電池充放電機構を解明

産業技術総合研究所(産総研)の朝倉大輔主任研究員らは、軟X線発光分光を用いてリチウムイオン電池充放電機構を詳細に解析する手法を開発した。 産総研、加工用レーザーのパワーを高精度に制御

産総研、加工用レーザーのパワーを高精度に制御

産業技術総合研究所(産総研)の沼田孝之主任研究員は、機械加工や鋼板溶接などに用いる高出力レーザーのパワーを高精度に制御するシステムを開発した。この技術はレーザービームの形状制御にも応用できる。 東工大ら、パワーデバイス内部の電界を直接計測

東工大ら、パワーデバイス内部の電界を直接計測

東京工業大学の岩崎孝之助教らによる研究グループは、新たな電界センサーを開発し、パワーデバイス内部の電界を直接計測することに成功した。 圧電性能を向上、RFスパッタ法でGaN薄膜作製

圧電性能を向上、RFスパッタ法でGaN薄膜作製

産業技術総合研究所(産総研)の上原雅人主任研究員らは村田製作所と共同で、RFスパッタ法を用いて、単結晶と同等の圧電性能を示すGaN(窒化ガリウム)薄膜を作製する方法を開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 太陽誘電26年度は営業利益91.2%増 AIサーバ/車載コンデンサー需要で

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

左側は一般的なSBD内蔵MOSFETの構造、右側は今回開発したトランジスター「SWITCH-MOS」の断面模式図 出典:産総研

左側は一般的なSBD内蔵MOSFETの構造、右側は今回開発したトランジスター「SWITCH-MOS」の断面模式図 出典:産総研 開発したデバイス「SWITCH-MOS」の内蔵ダイオードがオン状態における電圧分担 出典:産総研

開発したデバイス「SWITCH-MOS」の内蔵ダイオードがオン状態における電圧分担 出典:産総研 開発したデバイス「SWITCH-MOS」に内蔵したダイオードの順方向電流−電圧特性 出典:産総研

開発したデバイス「SWITCH-MOS」に内蔵したダイオードの順方向電流−電圧特性 出典:産総研 開発したデバイスSWITCH-MOSの順方向電流ストレス後のフォトルミネッセンス像 出典:産総研

開発したデバイスSWITCH-MOSの順方向電流ストレス後のフォトルミネッセンス像 出典:産総研