光変調器の試作例(マッハツェンダ変調器とリング変調器):福田昭のデバイス通信(152) imecが語る最新のシリコンフォトニクス技術(12)(2/2 ページ)

シリコン半導体のリング変調器とその性能

マッハツェンダ変調器の問題点は、180度の位相差を稼ぐためには一定以上の長さが必要なことだ。前述の試作例では、約1.5mmの長さを必要とした。これはシリコン半導体のダイ(チップ)にレイアウトするときに、かなりの不自由さを伴う。シリコンダイ面積に与える影響もそれなりに大きい。また、バイアス電圧が約10Vとかなり高いことも、シリコン面積の増加要因となる。

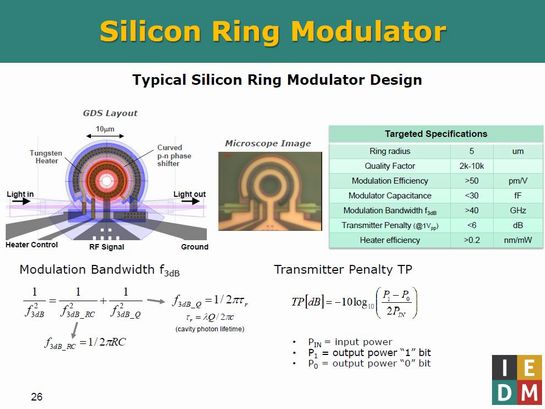

これに対して外形寸法が非常に小さく、またバイアス電圧が低くて済むのが「リング変調器」である。リング変調器はリング状のシリコン光導波路(リング共振器)における共振周波数(共振波長)が光路長によって決まる。直線状の光導波路に近接してリング共振器の光導波路をレイアウトすることで、共振波長に相当する光がリング共振器に閉じ込められ、直線状の光導波路では光強度が小さくなる。

ここでリング状のシリコン光導波路の円周に沿ってpn接合を形成し、バイアス電圧によって屈折率を変化させ、共振波長をずらす。するとバイアス電圧の高低によって直線状光導波路の光強度が変化する。このようにして光を変調する。

マッハツェンダ変調器と同様に、リング変調器でも光導波路の屈折率は温度に依存する。また寸法ばらつきによっても屈折率が変化する。そこでリング変調器も、温度調整用のヒーターを備える。

このようにして試作したリング変調器の設計仕様と性能の一例を示そう。リング共振器の直径は約10μm。変調効率(電気光学係数)は50pm(ピコメートル、10のマイナス12乗メートル)/V以上、変調帯域幅は40GHz以上である。透過損失(バイアス電圧(ピークツーピーク値)1Vのとき)は6dB以下、ヒーターの効率(共振波長のシフト量)は0.2nm/mW以上。

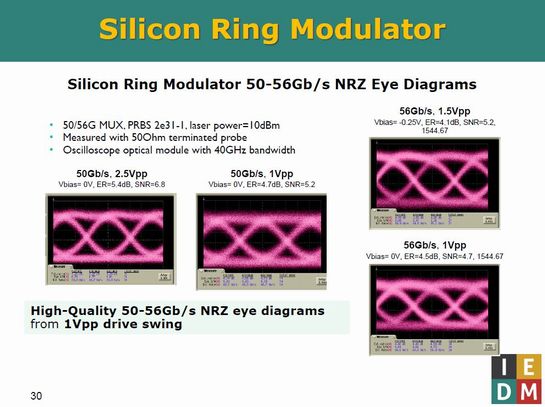

試作したリング変調器は、バイアス電圧(ピークツーピーク値)が1Vと低くても、50Gbpsあるいは56Gbpsと高い速度でNRZ信号を変調できている。

試作したリング変調器によって50Gbpsあるいは56Gbpsと高い速度でNRZ信号を変調したときの信号波形(アイパターン)。レーザー光源の出力は10mW。疑似ランダム符号列(PRBS)で変調をかけている。出典:imec(クリックで拡大)

試作したリング変調器によって50Gbpsあるいは56Gbpsと高い速度でNRZ信号を変調したときの信号波形(アイパターン)。レーザー光源の出力は10mW。疑似ランダム符号列(PRBS)で変調をかけている。出典:imec(クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

IEDMで発表されていた3D XPointの基本技術(前編)

IEDMで発表されていた3D XPointの基本技術(前編)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。 メモリ・アーキテクチャの基礎

メモリ・アーキテクチャの基礎

今回は、NANDフラッシュメモリ登場後のメモリ・アーキテクチャを見ていきながら、「CPUのメモリに対する要求」を考えていく。 NTT、小型で低損失の光変調器を開発

NTT、小型で低損失の光変調器を開発

NTTは、シリコンフォトニクス技術を用いた光変換器に、インジウムリン(InP)系化合物半導体を融合した、小型、低消費電力で低損失の光変調器を開発した。 埋め込みMRAMの磁気トンネル接合(MTJ)に要求される条件

埋め込みMRAMの磁気トンネル接合(MTJ)に要求される条件

多層配線の製造工程に磁気トンネル接合(MTJ)の製造プロセスを組み込むと、どのようなことがMTJに要求されるようになるのか。今回は、その要求を解説する。 微細化限界に達したフラッシュをMRAMで置き換え

微細化限界に達したフラッシュをMRAMで置き換え

埋め込みフラッシュメモリが直面する課題は、微細化の限界である。GLOBALFOUNDRIESは、2xnm以下の技術世代に向けた埋め込み不揮発性メモリとして、MRAM(磁気抵抗メモリ)を考えている。 低遅延の光アクセス技術、5G向けに活用可能

低遅延の光アクセス技術、5G向けに活用可能

NTTは、5G(第5世代移動通信)向けの技術として、低遅延の光アクセス技術を開発した。NTTビルなどに設置する光集約装置と基地局集約装置間の信号制御を連携させることで、データ送信の低遅延化が可能になるとする。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 次世代パワー半導体 「期待の5材料」の現在地

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- パワー停滞も光デバイス堅調、三菱電機の半導体部門