Intel、最上位FPGA「Stratix 10」の搭載カードを発表:データセンターアプリケーション向け

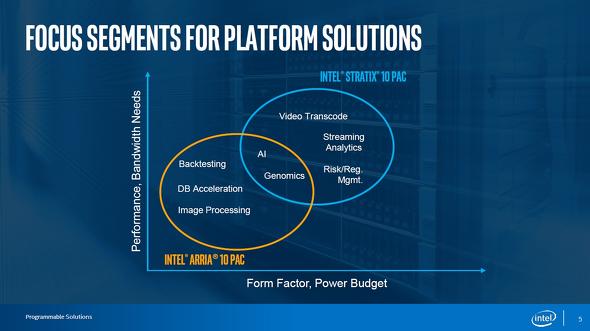

Intelは2018年9月25日(米国時間)、同社製FPGA「Stratix 10 SX」を搭載したプログラマブルアクセラレーションカード(PAC)を発表した。既に発表済みとなるミッドレンジFPGA「Arria 10」搭載版PACとともに、データセンターアプリケーション向けポートフォリオを拡充する。

Intelは2018年9月25日(米国時間)、同社製FPGA「Stratix 10 SX」を搭載したプログラマブルアクセラレーションカード(PAC)を発表した。発表済みとなるミッドレンジFPGA「Arria 10」搭載版PACとともに、データセンターアプリケーション向けポートフォリオを拡充する。

ビデオトランスコードやストリーミングアナリティクスを高速化

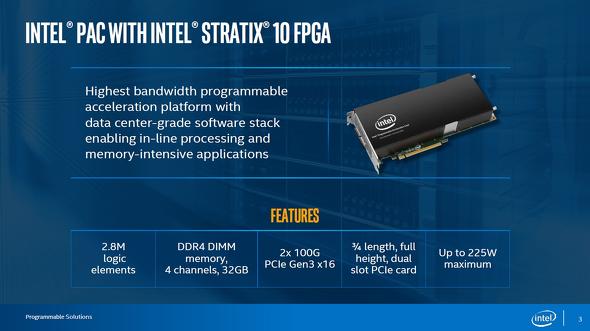

今回発表されたPACに搭載されるStratix 10 SXは、クアッドコアのArm Cortex-A53プロセッサと統合したSoC(System on Chip)で、ロジックエレメント数は約280万個。PACには、メモリとして32Gバイトの4チャンネルDDR4 DRAMを実装しており、Arria 10搭載版PACと比較して「メモリを多く必要とする処理にも向く」(同社)としている。

フォームファクターは、4分の3レングスでフルハイトのPCIe(PCI Express)カード。デュアルスロットを専有する。インタフェースではPCIe Gen3 x16と、2個の100Gビット/秒(bps)イーサネットを採用した。最大消費電力は225W。

同社では、Stratix 10搭載版PACの活用領域として、ビデオトランスコードや流れるデータをストレージに送る前に随時処理するストリーミングアナリティクス、金融におけるリスクマネジメント、AI(人工知能)やゲノミクスに有効だとしている。

関連記事

データ処理のボトルネック、FPGAで解決

データ処理のボトルネック、FPGAで解決

Intelのグループ会社である日本アルテラは、東京都内で「インテルFPGAテクノロジー・デイ(IFTD17)」を開催した。IoTからデータセンターまで、スマートにつながる未来を実現するためのFPGAソリューションを提案した。 “FPGAaaS”は業界に浸透するのか?(前編)

“FPGAaaS”は業界に浸透するのか?(前編)

「FPGAaaS(FPGA-as-a-Service:サービスとしてのFPGA)」のコンセプトが登場している。FPGAaaSは、FPGA業界にどのような影響を与えるのだろうか。 Alteraから「Intel FPGA」に向けて積極投資

Alteraから「Intel FPGA」に向けて積極投資

2015年にFPGA大手Alteraを買収したIntel。2016年8月30日にIntelのFPGA事業を担当する幹部が来日し、今後の製品開発方針やIntelとしてのFPGA事業の位置付けなどについて語った。 Arria 10を統合した「Xeon」、Intelが量産開始

Arria 10を統合した「Xeon」、Intelが量産開始

Intelは2018年5月17日(米国時間)、データセンターなど向けのプロセッサ「Xeonスケーラブルプロセッサ」について、FPGAを統合した「Xeon Gold 6138P」の量産を開始し、一部のベンダーに向けて提供を開始したと発表した。 アルテラのStratix10、新アーキテクチャ採用で従来比2倍のコア性能

アルテラのStratix10、新アーキテクチャ採用で従来比2倍のコア性能

アルテラは、ハイエンドのプログラマブルロジックデバイス「Stratix10FPGA&SoC」のアーキテクチャと製品概要を発表した。新製品は「HyperFlexアーキテクチャ」や「ヘテロジニアス3D SiP(System in Package)インテグレーション」技術を採用している。製造はIntelの14nmトライゲートプロセスを用いて行われる。 HBM 2対応メモリを統合、アルテラのFPGA

HBM 2対応メモリを統合、アルテラのFPGA

アルテラは、同社のハイエンドFPGA製品とSK Hynix製3D積層メモリチップを統合したヘテロジニアスSiP(System in Package)デバイス「Stratix 10 DRAM SiP」を発表した。DRAMを外付けしていた場合に比べ、メモリ帯域幅は最低10倍となる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増