光変調器を駆動する高速CMOS回路の試作事例:福田昭のデバイス通信(164) imecが語る最新のシリコンフォトニクス技術(24)(2/2 ページ)

» 2018年09月26日 10時30分 公開

[福田昭,EE Times Japan]

28nmのCMOS製造技術でドライバ回路を試作

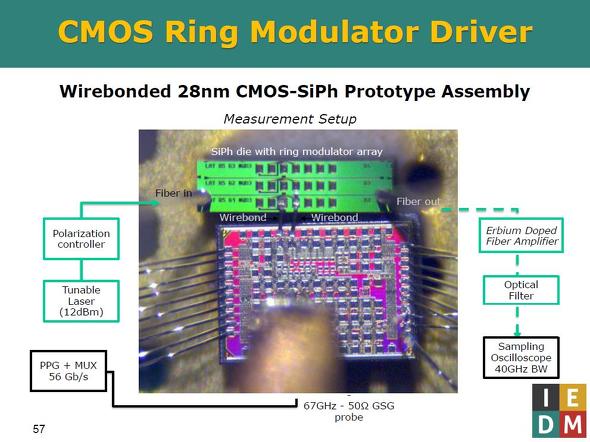

実際に28nm世代のCMOS製造技術によってドライバ回路を試作し、シリコンフォトニクスのリング変調器を駆動させてみた。ドライバ回路のシリコンダイとリング変調器のシリコンダイは、2本のボンディングワイヤで接続している。

リング変調器のシリコンダイを載せたモジュールは光送信器となっている。レーザーの出力を光ファイバー経由で受信し、リング変調器によって変調をかけ、光ファイバー増幅器へと送信する。光ファイバー増幅器の出力を電気信号に変換してサンプリングオシロスコープで観測する。

CMOSドライバ回路には、パルスパターン発生器とマルチプレクサによって最大で56Gbpsの駆動信号を外部から入力する。

電源電圧1.1Vで50Gpbsの動作を確認

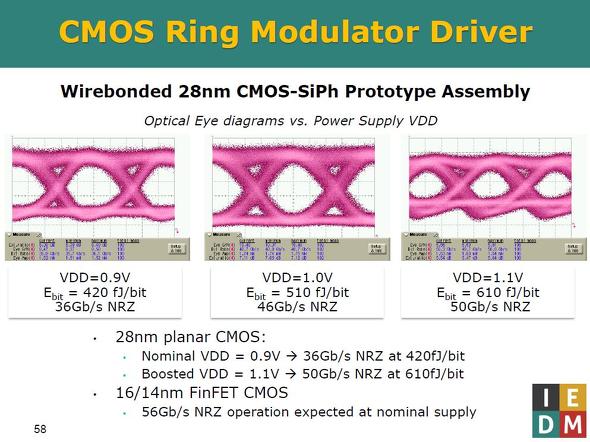

上記のようなセットアップで電源電圧を変化させ、NRZ符号のドライブ速度とビット当たりのエネルギー消費を比較してみた。電源電圧は0.9Vを標準電圧と想定し、標準電圧から高い電圧へと電源電圧を変更した。具体的には電源電圧が1.0Vの場合と、1.1Vの場合を試した。

その結果、電源電圧が0.9V(標準電圧)のときは、NRZ符号を36Gbpsでドライブできた。電源電圧を1.1Vに高めたときは、50Gbpsでドライブできるようになった。ただしビット当たりの消費エネルギーは増加した。

実験結果から、CMOSドライバ回路の製造技術を16nm/14nmのFinFET技術に微細化すれば、標準電圧でも56Gbpsでドライブできる見通しが得られたという。

28nm技術によって試作したCMOSドライバ回路でリング変調器を駆動したときの信号波形。左はCMOSドライバ回路の電源電圧が0.9Vのとき、中央は電源電圧が1.0Vのとき、右は電源電圧が1.1Vのとき。出典:imec(クリックで拡大)

28nm技術によって試作したCMOSドライバ回路でリング変調器を駆動したときの信号波形。左はCMOSドライバ回路の電源電圧が0.9Vのとき、中央は電源電圧が1.0Vのとき、右は電源電圧が1.1Vのとき。出典:imec(クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

光送受信器の構造と性能向上手法

光送受信器の構造と性能向上手法

光送受信器の構造と性能向上(スケーリング)について解説する。性能向上の手法は主に、高速化、多値化、多チャンネル化の3つの方向性がある。 光変調器の試作例(マッハツェンダ変調器とリング変調器)

光変調器の試作例(マッハツェンダ変調器とリング変調器)

「マッハツェンダ変調器(MZ変調器)」と「リング変調器」の試作例を取り上げ、構造と性能を紹介する。 シリコンフォトニクスで使われる主な光変調器

シリコンフォトニクスで使われる主な光変調器

前回、光信号の振幅や位相などを連続的に変化させるデバイス「光変調器」の基礎を説明した。今回からは、光変調器の具体的な解説に入る。 IoE向けの超低消費電力無線チップ

IoE向けの超低消費電力無線チップ

今回はセッション24〜26を紹介する。「ワイヤレス通信」がテーマとなっているセッション24では、IoE(Internet of Everything)向けの低消費電力無線チップの発表が相次ぐ。ソニーとソニーLSIデザインが開発した、消費電力が1.5mW〜2.3mWと低いGNSS(全地球航法衛星システム)受信器などが発表される。 超高密度のSRAM技術と超広帯域のDRAM技術

超高密度のSRAM技術と超広帯域のDRAM技術

セッション17とセッション18のテーマはメモリだ。セッション17では、Samsung Electronicsが、10nmのFinFETを用いた高密度SRAMの開発成果を披露する。メモリセルの面積が0.04μm2と、過去最小のSRAMセルを実現している。 マイコン市場、IoTを追い風に安定成長

マイコン市場、IoTを追い風に安定成長

米国の市場調査会社であるIC Insightsによると、マイコン(MCU)市場は今後5年の間、主にセンサーの普及が進んでいることや、IoTの台頭などを受け、安定成長を続ける見込みだという。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

Special SitePR

あなたにおすすめの記事PR