3nm止まりか1nmか、微細化はレジスト開発が鍵:半導体ロードマップの展望(2/2 ページ)

imecとKMLabsは、レジスト開発の専門組織を立ち上げ

ベルギーの研究機関imecと、レーザー専門企業KMLabsは、次世代EUVシステム向けのレジスト開発を後押しするための取り組みとして、「AttoLab」を共同設立すると発表した。ピコ秒あるいはアト秒で測定される時間枠の中で、レジストがどのように光子を吸収、イオン化するのかを明らかにしていくという。

imecの主任科学研究員であるJohn Petersen氏は、「サプライヤーとの協業によって新材料を開発し、次のレベルまで前進していくことにより、放射線化学の詳細について学ぶことができる。また、量子現象についても考察していく。純粋科学でありながら、取り組みの中から新技術が生み出される可能性がある」と述べている。同氏は、新型ラボに関する論文を共同執筆している。

レジストは、確率変数とされるランダムエラーを削減するための一つの方法である。古くから存在していた問題ではあるが、5nmプロセスの開発を進めるにつれ、その影響は大きくなっている。Yen氏は、「ASMLは、歩留まりを脅かすような問題にも対応することができる」と強気な見解を示している。

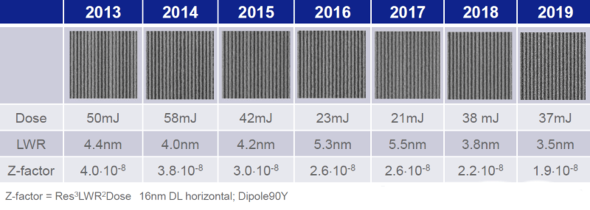

同氏は、「確率変数については現在、193nmのリソグラフィの時よりも重大な課題となっているが、高いドーズ(露光量)を実現することで対応は可能だ。当社のロードマップは、500Wシステムの実現を目指しているため、光源を高めることによって、高NA(開口数)システムの画像品質を実現し、確率変数の問題に対応するための準備を整えることができる」と述べている。

imecで計測分野を専門とするPhillipe Leray氏は、あまり楽観視はしていないようだ。同氏は、「近い将来、欠点に関する問題に取り組む必要に迫られるだろう。残り時間が迫る中、まだ解決策を見いだせそうにない」と述べる。

Armのフェローを務めるRob Aitken氏は、「設計者たちは、ロジックチップの10億個の物理的な接点の中の一つに欠陥が存在する可能性をなくそうと、取り組みを進めているところだ。そのための方法として、いくつか候補を用意できている」と述べている。

一部のパネリストからは、積層チップの成功を踏まえて、3D(3次元)構造に注力すべきだとする声が上がっている。その中の1人であるAitken氏は、「3D設計はかなり複雑化するため、新しいマイクロアーキテクチャが必要だ。しかし、まだ誰もその取り組みを達成できておらず、電力供給やクロッキングが難しくなるということに注目するにとどまっている」と述べる。

また同氏は、「設計者たちは既に、微細化の実現に向け、標準的な12トラックセルや9トラックセルから4トラックだけを使用するセルへ移行するための準備を進めている。このような取り組みは、数年前までは全く不可能だったが、今や実現可能になってきた」と付け加えた。

実際に、非常に難しい取り組みであるため、半導体技術のあらゆる分野について検討が行われているさなかだ。コンサルタントであるErik Hosler氏は、「われわれは現在、あらゆる種類の最先端パターニングについて検討している。EUVは、私が現在担当しているカンファレンスの、最先端パターニングのセクションから出現した技術だ」と述べる。

かつてGLOBALFOUNDRIESでEUVの専門家として務めた経歴を持つHosler氏は、「われわれは2018年に、MEMSとMOEMS(Micro Optical Electro Mechanical System)を追加した。今後も、疑問を提起する対象を量子まで広げていくつもりだ。さまざまな素晴らしい取り組みが進められることにより、何か新しいものが登場するだろう」と述べている。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか

10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか

Intelは2016年以降、今日に至るまで、10nmプロセスを立ち上げることができていない。一方で、配線ピッチは同等であるはずの、TSMCとSamsung Electronicsの7nmプロセスは計画通りに進んでいる。ではなぜ、Intelは10nmプロセスの立ち上げに苦戦しているのだろうか。 TSMC、フォトレジスト材の品質不良で5億ドル超の損失

TSMC、フォトレジスト材の品質不良で5億ドル超の損失

TSMCは、台湾南部にある同社最大規模の工場の一つである「Fab 14B」において、フォトレジスト材料の品質不良のために、ウエハーを廃棄処分したことを明らかにした。 ミニマルファブ、半導体チップの試作も活発に

ミニマルファブ、半導体チップの試作も活発に

ミニマルファブ推進機構は、「SEMICON Japan 2018」で、「ミニマルファブ、先端へ」をキャッチフレーズに、新開発のミニマルファブ向け製造装置や、ミニマルファブ装置で製作した実チップなどを展示した。 ディスコ、「切る、削る、磨く」工程の効率向上へ

ディスコ、「切る、削る、磨く」工程の効率向上へ

ディスコは、「SEMICON Japan 2018」で、後工程の自動化、作業効率の改善に向けた「並列加工搬送システムver.2」や、スマートフォンで「精密加工装置を監視、制御できるシステム」などを提案した。 遅れていたIntelの10nmチップ、出荷開始のメドが立つ

遅れていたIntelの10nmチップ、出荷開始のメドが立つ

Intelは、「10nmプロセスの歩留まりの改善を進めている」と述べ、2019年のホリデーシーズンまでに10nmチップを出荷する計画をあらためて表明した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

システムを開発するエンジニア 出典:ASML

システムを開発するエンジニア 出典:ASML