インテル、5G向けのアクセラレーションカード:新たな収益源を生み出す

インテルは、5G(第5世代移動通信)コアネットワーク用装置などに搭載し、高速処理を実現するアクセラレーションカード「FPGA PAC N3000」を発表した。

新サービスの提供や将来の拡張性に備える

インテルは2019年3月7日、5G(第5世代移動通信)コアネットワーク用装置などに搭載し、高速処理を可能にするアクセラレーションカード「FPGA PAC N3000」を発表した。汎用サーバ上のCPUと同カードを組み合わせることで、CPUの使用率を50%に抑えることができ、そのリソースを将来の機能拡張や新サービスに振り向けることが可能になるという。

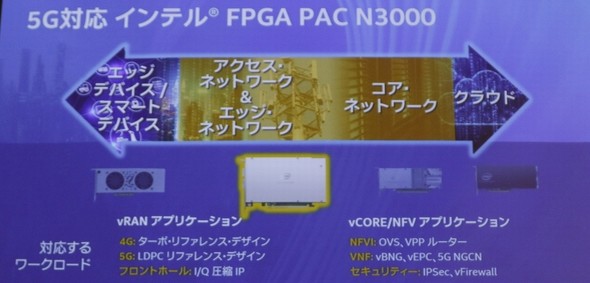

FPGA PAC N3000は、高いスループットと低遅延、広帯域幅などが要求される5Gコアネットワークや仮想化無線アクセスネットワーク用装置に向けた製品。FPGA「Intel Arria 10」や、2個のイーサネットコントローラ「XL710」、最大9GバイトのDDR4と144MバイトのQDR IVメモリ、電源IC「Enpirion」および、これらを管理するFPGA「Intel MAX 10」などをボード上に実装している。

また、仮想化無線アクセスネットワーク(vRAN)や仮想ブロードバンドネットワークゲートウェイ(vBNG)、仮想Evolved Packet Core(vEPC)、インターネットプロトコルセキュリティ(IPSec)、ベクトルパケット処理(VPP)など、ネットワーク機能アクセラレーションワークロード向けのレファレンスIPコアも提供する。

インテルのプログラマブルソリューションズ営業本部データセンター&コミュニケーション統括部で統括部長を務める渡海博史氏は、「PAC N3000はコアネットワークとアクセスネットワーク&エッジネットワークの領域をカバーする。これまで、汎用サーバ上のCPUで処理していた機能をFPGAで実行させる。これによってCPUの演算負荷を50%削減できるアプリケーションもある。このリソースを新たなサービスの提供などに振り向けることが可能となり、サービスプロバイダーの収益改善にもつながる」と話す。さらに、FPGAを搭載することで、カスタマイズや新たな標準規格などにも柔軟に対応することが可能なことも強調した。

関連記事

Intelが新しい3D積層チップ技術「Foveros」を発表

Intelが新しい3D積層チップ技術「Foveros」を発表

Intelは、新しい3Dパッケージング技術「Foveros」のデモを披露した。2019年後半には提供できる見込みだという。Intelは、このFoverosの開発に20年間を費やし、ロジックとメモリを組み合わせた3D(3次元)のヘテロジニアス構造でダイ積層を実現した。 Intel 10nmプロセスの遅れが引き起こしたメモリ不況

Intel 10nmプロセスの遅れが引き起こしたメモリ不況

2018年、メモリ市場の成長に暗雲が立ち込め、メモリ不況が避けられない事態となった。アナリストらは、メモリの過剰供給による価格の下落を要因として指摘しているが、どうも腑に落ちない。そこで筆者は、Intelの10nmプロセスの遅れという点から、メモリ不況の要因を探ることにした。 インテル「第9世代Core」プロセッサ、クロックは最大5GHz

インテル「第9世代Core」プロセッサ、クロックは最大5GHz

インテルは2018年10月11日、デスクトップ向けの最新プロセッサ「第9世代インテル Coreプロセッサー(以下、第9世代Coreプロセッサー)」を発表した。ゲーミング向けに設計された製品で、「Core i9」「Core i7」「Core i5」の3種がある。既に予約を開始していて、10月19日に発売される。 遅れていたIntelの10nmチップ、出荷開始のメドが立つ

遅れていたIntelの10nmチップ、出荷開始のメドが立つ

Intelは、「10nmプロセスの歩留まりの改善を進めている」と述べ、2019年のホリデーシーズンまでに10nmチップを出荷する計画をあらためて表明した。 戦艦Intelの方向転換なるか ―― 新CEOの使命

戦艦Intelの方向転換なるか ―― 新CEOの使命

Bob Swan氏は、米国最大の半導体メーカーであるIntelで暫定CEOを7カ月間にわたり務めた後、正式にCEOに就任することが決まった。同社は現在、50年間の歴史の中で、最も重大な岐路に立たされている。依然として、半導体市場における優位性を確保しているが、その優位性をあとどれくらいの間にわたって維持できるのかは不明だ。アナリストたちは、「Intelは、差し迫った状況に対して重大な決断を下すことにより、同社が今後、どれくらい耐えられるのかが決まるだろう」とみているようだ。 Intelの5Gチップ開発をAppleが後押し

Intelの5Gチップ開発をAppleが後押し

Intelが、統合型5G(第5世代移動通信)モデム「XMM 8160」の開発計画を発表した。市場が最高の状態に達するとみられる2020年の実現を目指すという。これを受けてQualcommは、統合型チップセット開発の取り組みを加速させることにより、2019年を通して、5Gのみに対応したモデム向けの数少ない顧客の大半を確保していくのではないかとみられている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- Cerebrasが上場 NVIDIA対抗馬の「試金石」となるか

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

FPGA PAC N3000を手にする渡海博史氏

FPGA PAC N3000を手にする渡海博史氏