ミニマルファブ方式で、宇宙用集積回路を試作:2層アルミ配線プロセスを適用

宇宙航空研究開発機構(JAXA)と産業技術総合研究所(産総研)は、半導体チップの少量生産に適したシステム「ミニマルファブ」を用いて、宇宙機搭載用の集積回路を試作し、その動作実証に成功した。

全自動で動作、回路設計者1人でデバイスを製造

宇宙航空研究開発機構(JAXA)と産業技術総合研究所(産総研)は2019年5月、半導体チップの少量生産に適したシステム「ミニマルファブ」を用いて、宇宙機搭載用の集積回路を試作、その動作実証に成功したことを発表した。

ミニマルファブは、直径0.5インチ(12.5mm)のウエハーを用いて、半導体チップを短期間で製造することが可能なシステムである。局所クリーン化生産システムにより、スペースや設備環境、投資額に制限がある研究室などでも比較的容易に導入できる。

ミニマルファブ対応の製造装置は、既に商用販売されているが、これまで製造実績があるのは単体トランジスターや小規模の発振回路などにとどまっていた。そこでJAXAと産総研は、宇宙機に搭載する半導体チップの製造に向けて共同研究を行ってきた。

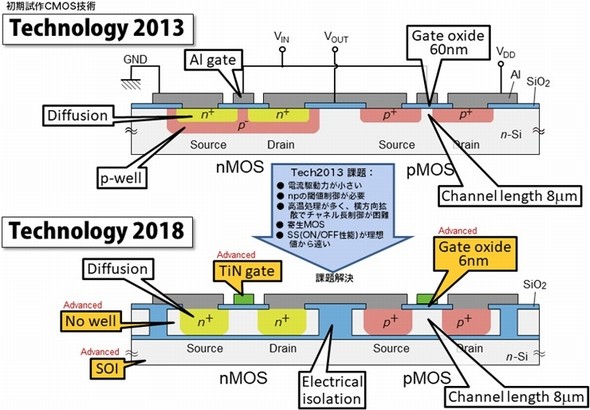

産総研は、これまで蓄積してきた製造技術に加え、フルミニマルSOI-CMOS 2層アルミ配線プロセスを新たに開発した。「Technology 2018」と呼ぶこの技術は、プロセスに必要な技術情報と一連の動作手順が全て電子化されているという。このため、作業者(設計者)はプロセス情報を知らなくても、スタートボタンを1回押すだけで半導体チップを製造することができる。

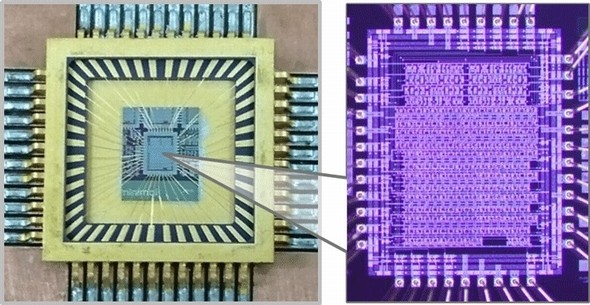

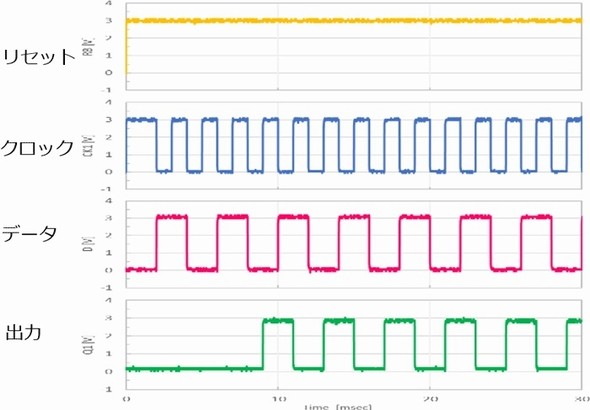

JAXAは、まずNANDゲートを設計、試作してその動作に成功した。続いて1000トランジスター規模の4ビットシフトレジスターおよび、I/O回路を設計した。これをTechnology 2018技術で製造し、正常に動作することを確認した。特に、耐放射線集積回路が製造可能かどうかを確認するため、4ビットシフトレジスターのDフリップフロップはクロックゲートタイプにしたという。

今回の成果により、宇宙機向け集積回路の製造においてミニマルファブ方式が有用性であることを確認した。今後は宇宙用半導体チップの実用化に向けた検討を行う。さらに、IoT(モノのインターネット)向けデバイス製造におけるミニマルファブ方式の応用などを展開する考えだ。

関連記事

ミニマルファブ、半導体チップの試作も活発に

ミニマルファブ、半導体チップの試作も活発に

ミニマルファブ推進機構は、「SEMICON Japan 2018」で、「ミニマルファブ、先端へ」をキャッチフレーズに、新開発のミニマルファブ向け製造装置や、ミニマルファブ装置で製作した実チップなどを展示した。 産総研、大面積ダイヤモンドウエハー実現可能に

産総研、大面積ダイヤモンドウエハー実現可能に

産業技術総合研究所(産総研)は、マイクロ波プラズマCVD法を用い、クラックがない体積1cm△△3△△級の単結晶ダイヤモンド作製に成功した。インチサイズのウエハー実現に大きく近づいた。 産総研、5G用FPC向け高強度異種材料接合技術開発

産総研、5G用FPC向け高強度異種材料接合技術開発

産業技術総合研究所(産総研)と新技術研究所は共同で、5G(第5世代移動通信)用の低損失基板に向けた「高強度異種材料接合技術」を開発した。 産総研、物理リザバー計算用AIハードウェア実現へ

産総研、物理リザバー計算用AIハードウェア実現へ

産業技術総合研究所(産総研)らの研究グループは、スピントルク発振素子を用いた「物理リザバー計算」において、短時間記憶容量を向上させることに成功した。IoT端末やロボット向け小型AIハードウェアの開発に弾みをつける。 産総研、簡単な工程でCNT透明導電膜を作製

産総研、簡単な工程でCNT透明導電膜を作製

産業技術総合研究所(産総研)の研究グループは2019年1月、簡単な工程で高い導電率と耐久性を有するカーボンナノチューブ(CNT)透明導電膜の作製方法を開発した。 産総研、170GHzまで材料の誘電率を高精度に計測

産総研、170GHzまで材料の誘電率を高精度に計測

産業技術総合研究所(産総研)は、10G〜170GHzの広帯域にわたって、エレクトロニクス材料の誘電率を高い精度で測定できる技術を開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

既存メガファブとミニマルファブの違い 出典:産総研

既存メガファブとミニマルファブの違い 出典:産総研 ミニマルファブ向けに開発された実用SOI-CMOS Technology 2018 出典:産総研

ミニマルファブ向けに開発された実用SOI-CMOS Technology 2018 出典:産総研

上図は試作した集積回路のチップ写真、下図は4ビットシフトレジスターの測定結果 出典:産総研

上図は試作した集積回路のチップ写真、下図は4ビットシフトレジスターの測定結果 出典:産総研