「3D XPointメモリ」開発のオープン・モードとステルス・モード:福田昭のストレージ通信(148) 半導体メモリの技術動向を総ざらい(9)(1/2 ページ)

今回は、「3D XPointメモリ」の研究開発が、オープン・モードで始まり、後半はステルス・モードとなっていたことを説明する。

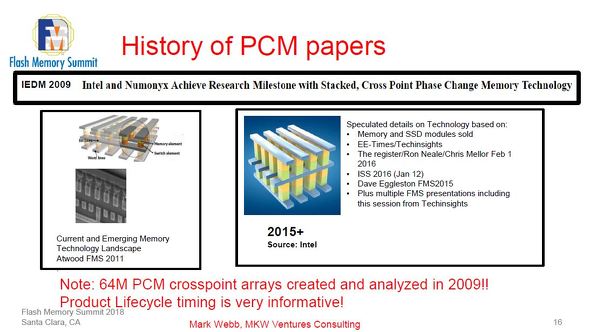

「3D XPointメモリ」の基本技術は2001年と2009年に学会で発表

2018年8月に米国シリコンバレーで開催された、フラッシュメモリとその応用製品に関する世界最大のイベント「フラッシュメモリサミット(FMS:Flash Memory Summit)」でMKW Venture Consulting, LLCでアナリストをつとめるMark Webb氏が、「Annual Update on Emerging Memories」のタイトルで講演した半導体メモリ技術に関する分析を、シリーズでご紹介している。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、相変化メモリ(PCM)が2013年に市場から一度消えた後に、2015年に「3D XPointメモリ」で劇的に復活したことをご報告した。今回は、「3D XPointメモリ」の研究開発が始めはオープン・モードであり、後半に入ってステルス・モードとなっていたことをご説明する。

本シリーズの第5回と第6回でご報告したように、次世代半導体製品の研究開発では、前半が研究成果の一部を公表するオープン・モード、後半がひそかに研究開発を進めるステルス・モードであることが少なくない。「3D XPointメモリ」の研究開発でも、オープン・モードの時代があったとみられる。

IntelとMicron Technology(以降はMicronと表記)が「3D XPointメモリ」の共同開発を発表したのは、2015年7月である。その5年半ほど前の2009年12月に、国際学会IEDMでIntelとNumonyx(IntelとSTMicroelectronicsの合弁企業、後にMicronによって買収された)がクロスポイント構造の相変化メモリ(PCM)を試作発表していたのだ。発表の概要は本コラムの姉妹コラム「福田昭のデバイス通信」で2016年1月にご紹介している(関連記事:「IEDMで発表されていた3D XPointの基本技術(前編)」)。

このとき発表されたクロスポイント構造のPCMは1層で、記憶容量は64Mビットだった。90nm世代の製造技術によって第2層金属配線と第3層金属配線の間に、クロスポイント構造のメモリセルアレイを作り込んだ。そしてセレクタ技術は、OTS(Ovonic Threshold Switch)だった。PCMとOTSの組み合わせという要素技術は、「3D XPointメモリ」と同じである。PCMとOTSの材料は公表していない。

メモリセルのスイッチング(書き込み)時間はリセット動作(高抵抗状態への相変化)のときに最短で9ナノ秒とかなり短い。そして読み書きのサイクル寿命(セット(低抵抗)状態でのしきい電圧で評価)は100万回に達していた。

さらにさかのぼると、2001年12月に国際学会IEDMでIntelとOvonyx社(相変化メモリの開発ベンチャー)が、PCM技術を共同発表していた。PCMのカルコゲナイド合金はGeSbTeである。この3元素の組み合わせは、「3D XPointメモリ」のPCMと変わらない。ただしIEDMでは組成比を公表していないので、組成比が同じであるかどうかは、不明である。

2009年12月の国際学会IEDMでクロスポイント構造のメモリが発表された後は、国際学会や学会論文誌などで「3D XPointメモリ」に関連する技術が発表された痕跡は見当たらない。すなわち、ステルス・モードに入ったとみられる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長