一度消えたPCMが「3D XPointメモリ」で劇的にカムバック:福田昭のストレージ通信(147) 半導体メモリの技術動向を総ざらい(8)(2/2 ページ)

» 2019年06月03日 10時30分 公開

[福田昭,EE Times Japan]

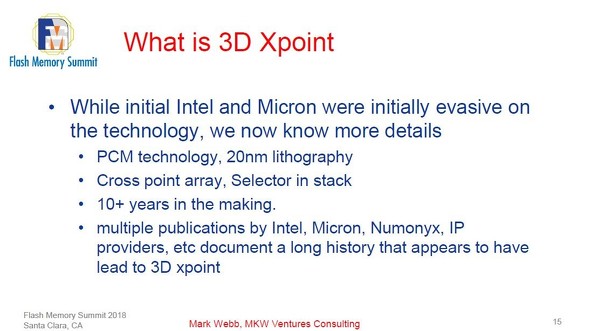

10年以上の歳月をかけて開発された「3D XPointメモリ」

「3D XPointメモリ」について公式に発表された情報はあまり多くない。メモリセルアレイは2層の3次元クロスポイント構造であること、メモリセルは1個の記憶素子と1個のセレクタ(セル選択スイッチ)を積層した構造であること、シリコンダイの記憶容量は128Gビットであること、10年を超える歳月をかけて共同開発したこと、くらいである。現在に至るも、128Gビット・チップの要素技術が国際学会で本格的に発表されたことはない。

一方でシリコンダイを元素分析する技術を備えた調査会社TechInsigtsにより、IntelのHDDキャッシュ製品から取り出した128Gビット「3D XPointメモリ」チップの解析結果が2017年8月のフラッシュメモリサミット(FMS)で発表された。製造技術は20nmのCMOS技術と1層多結晶シリコン配線技術、5層金属配線技術(クロスポイントのワード線とビット線を除く)である。クロスポイント構造のメモリセルアレイは、第4層金属配線と第5層金属配線の間に作り込まれた。

「3D XPointメモリ」の概要。開発企業であるIntelとMicron Technologyが公式に発表した情報以外に、他社が分析した情報を含んでいる。出典:MKW Venture Consulting, LLC

「3D XPointメモリ」の概要。開発企業であるIntelとMicron Technologyが公式に発表した情報以外に、他社が分析した情報を含んでいる。出典:MKW Venture Consulting, LLCシリコンダイ面積は206.5mm2(16.16mm×12.78mm)とかなり大きく、メモリセル面積は0.0015μm2と小さい。メモリセルの記憶素子はPCM、セレクタはOTS(Ovonic Threshold Switch)であること、PCMの材料はGeSbTeSi(組成は0.12:0.29:0.54:0.05)、OTSの材料はSeAsGeSi(組成は0.44:0.29:0.10:0.17)であることも明らかになった。

(次回に続く)

関連記事

次世代メモリの市場予測と3D XPointメモリの現状

次世代メモリの市場予測と3D XPointメモリの現状

今回は、次世代メモリのうち、MRAM(磁気抵抗メモリ)とクロスポイントメモリ(XPoint)について、市場予測と開発状況を説明する。 「3D XPoint」、Intelは強気もMicronは手を引く?

「3D XPoint」、Intelは強気もMicronは手を引く?

IntelとMicron Technology(以下、Micon)が、共同開発プログラムを終了する予定であると発表した。両社が共同開発しているメモリ「3D XPoint」の将来に何が待ち受けているのかは、誰にその問いかけをするかによって答えが異なるだろう。 「3D XPoint」は相変化メモリか――特許から詮索

「3D XPoint」は相変化メモリか――特許から詮索

Intel(インテル)とMicron(マイクロン)がこのほど発表した不揮発性メモリ「3D XPoint」は本当に相変化メモリの1つなのか? 筆者が特許をウェブで検索したところ、この見方を裏付ける結果となった。 次世代メモリ技術の最有力候補はPCMとMRAM、ReRAM

次世代メモリ技術の最有力候補はPCMとMRAM、ReRAM

今回は、次世代メモリの立ち位置を再確認した上で、相変化メモリ(PCM)、磁気抵抗メモリ(MRAM)、抵抗変化メモリ(ReRAM)という3つの最有力候補について解説する。 現行世代メモリと次世代メモリの違い

現行世代メモリと次世代メモリの違い

フラッシュメモリとその応用製品に関する世界最大のイベント「フラッシュメモリサミット(FMS:Flash Memory Summit)」。最近のFMS(2018年8月に開催)で公表された情報の1つに、半導体市場調査会社MKW Venture Consulting, LLCでアナリストを務めるMark Webb氏が「Annual Update on Emerging Memories」のタイトルで述べた、半導体メモリの技術動向に関する講演がある。その内容が興味深かったので、講演の概要をシリーズでお届けする。 既存のメモリと次世代のメモリを比較する

既存のメモリと次世代のメモリを比較する

今回は、DRAMやNANDフラッシュメモリなど既存のメモリと、MRAM(磁気抵抗メモリ)やReRAM(抵抗変化メモリ)といったエマージング・メモリ(次世代メモリ)の特徴を比較する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR