5Gチップには「シリコン+III-V族」が最適?:シンガポールとMITの研究チーム

5G向けに、IBMや米MIT(マサチューセッツ工科大学)などが、シリコンとIII-V族半導体を融合したチップを開発している。

シリコンと化合物半導体を融合させる

現在のほとんどのデバイスでは、コンピューティングにシリコンベースのCMOSチップが使用されている。だが、高度な通信システムでは、シリコンは限界に近づいており、熱的な問題が生じる恐れがある。市場に投入されている既存の5G(第5世代移動通信)スマートフォンが、使用中に非常に高温になり、電源が落ちるのは、これが原因だ。

こうした問題を回避するために、IBMや香港科技大学(Hong Kong University of Science and Technology)、MIT(マサチューセッツ工科大学)などがシリコンと化合物半導体の融合を試みている。

将来的に、“センサーを搭載し、データをコントロールセンターに無線で送信する”という、いわゆるIoT(モノのインターネット)機器は増加の一途をたどる。これはつまり、RFや低消費電力、小型のフォームファクタを組み合わせる必要があるということだ。これら全ての目的を達成する明確で有望なアプローチの一つは、シリコンCMOSの機能とIII-V族半導体を組み合わせた単一チップを作製することだ。

III-V族半導体材料には、窒化ガリウム(GaN)やインジウムガリウムヒ素(InGaAs)などがある。これらの材料固有の特性は、オプトエレクトロニクス(LEDなど)や通信に非常に適しているため、システム全体の効率が向上する。

IoTを実現するインフラとしての「5G」

5Gは、単に「4Gの高速版」というわけではない。5Gは、IoTを実現するためのインフラ候補と位置付けられている。

5Gネットワークは、高性能なクラウドアプリサービス、つまり、スマートシティーや自動運転車、新しい産業プラットフォームを有するインテリジェントなコネクテッド社会を実現する鍵だ。その全てを実現するには、要件に沿ったICを開発することが必須だが、そのためにはたくさんの設計作業やテスト、測定を行わなければならない。最も困難な障壁は、標準規格の継続的な改善やミリ波技術の採用、コスト管理などである。

MITとシンガポール国立研究財団(National Research Foundation of Singapore)が共同設立した研究施設であるSingapore-MIT Alliance for Research and Technology(SMART)は、高性能III-V族デバイスと統合したシリコン回路を製造する、商業的に実現可能な方法の開発に成功したと発表した。

SMARTのLow Energy Electronic Systems(LEES)Interdisciplinary Research Group(低エネルギー電子システム学際研究グループ、以下LEESグループ)でシニアイノベーションマネジャーを務めるFayyaz Singaporewala氏は、「現在のほとんどのデバイスは、シリコンベースのCMOSチップを採用してコンピューティングを実行している。だが、シリコンベースのCMOSチップは、照明や通信には効率が低く、発熱する」と述べている。

GaNデバイスの電力密度は上がっており、フェーズドアレイアプリケーションやその他の分野に採用されるデバイスの数は増加している。コストも、予算が重視される民生市場でも採算の取れるレベルになりつつある。これらの技術によって、高速コンバーターとマイクロ波部品を、パワーアンプやバイアス回路とともに単一のダイに集積することも可能になるとする。

SMARTのLEESグループでシニアサイエンティフィックディレクターを務めるKenneth Lee氏は、「シリコンCMOS技術の電力付加効率(PAE)は最大で20%だが、GaNデバイスは50%以上を達成できる。一方、シリコンCMOS技術には、(オンチップデジタル制御や適応マッチング、デジタルプリディストーション[DPD]などの)追加機能を高集積できるという利点がある。SMARTの技術は、5G技術に重要となるこれらの長所をどちらも活用できるようにする」と述べている。

5Gでは、最高レベルのデータ転送速度を提供するだけでなく、レイテンシ(遅延時間)を1ミリ秒未満に抑える必要がある。インターネットプロトコルの特性から、データ転送速度を高めるにはレイテンシの短縮が不可欠である。特に、通信を活用した安全性の向上が重要となる自動車では、レイテンシの短縮が死亡事故の危険性を大きく減らすことにつながるだろう。

Lee氏は、「現在の技術は5Gの要件に対応できないが、SMARTの新デバイスであれば、それが可能だ。SMARTの技術は、今後登場する複雑なモバイルデバイスの厳しい電力要件と、限られた予算の範囲内で、5Gの仕様に適したチップの設計を可能にするだろう」と述べている。

SMARTが発表したデバイスは、別々の基板上に生成したシリコンとIII-V族の2つの層をベースにしている。このプロセスでは既存の製造装置を使用できるので、コストを低く抑えることができるという。

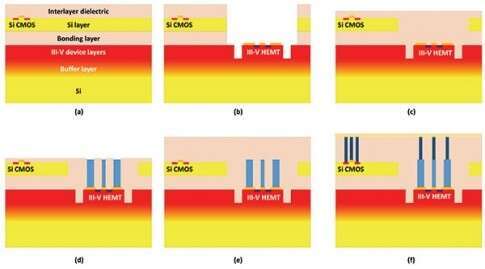

(a)厚さ1μmのシリコンCMOS層が、エピタキシーを使用して製造されたIII-V-on-Siliconウエハーに接合されている(b)下層のIII-V族層を露出させるために、CMOSのない領域にウィンドウが開かれ、III-V族デバイスが形成される(c)誘電体が形成される(d)III-V族デバイスに接続するためのW(タングステン)プラグが形成される(e)誘電体層はCMP(化学機械研磨)によって平たん化される(f)シリコンCMOSとIII-Vデバイスは一般的な方法で接続されて、統合が完了する。

SMARTは、この新しいシリコン-III-V族の融合チップを2020年に実用化し、2021年には製品に搭載されることを目指して開発を進めていく。

【翻訳:滝本麻貴、編集:EE Times Japan】

関連記事

第5世代(5G)移動通信システムが2020年代の通信を支える

第5世代(5G)移動通信システムが2020年代の通信を支える

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」の概要をシリーズで伝えている。今回から「第5世代(5G)移動通信システム」の内容を説明していく。 インドがLPWANの導入を加速、スマートシティー実現へ

インドがLPWANの導入を加速、スマートシティー実現へ

インドは現在、国内で100のスマートシティーを実現するという政府目標を遂行中だが、4000のスマートビレッジやスマートタウン、スマートシティーの実現に向けて、プログラムの第2フェーズである「Smart City Mission 2.0」の施行を検討しているという。 サブ6GHz/ミリ波の5Gモジュール、技適認証済み

サブ6GHz/ミリ波の5Gモジュール、技適認証済み

菱洋エレクトロは「CEATEC 2019」(2019年10月15〜18日、幕張メッセ)で、5G(第5世代移動通信)をサポートするモジュールを紹介した。 TSMC、5G好調で設備投資150億米ドルに引き上げ

TSMC、5G好調で設備投資150億米ドルに引き上げ

TSMCは、5G(第5世代移動通信)スマートフォンおよび関連ネットワーク機器の見通しが改善されたことを受け、2019年の設備投資額を150億米ドルに引き上げたことを明らかにした。 AppleがIntelのスマホ向けモデム事業を買収へ

AppleがIntelのスマホ向けモデム事業を買収へ

Appleは2019年7月25日(米国時間)、Intelのスマートフォンモデム事業を買収することで合意したと発表した。買収金額は約10億米ドルとされている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- ヒューマノイドはどこまで現実になっているのか

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し