ピン数の少ないDRAM、エッジAIをサポート:これも次世代メモリの一つ?

これまで次世代メモリに関しては、さまざまな議論がなされてきた。例えば、「IoT(モノのインターネット)の登場によって生み出されたビジネスチャンスにどう対応するのか」「SRAMのような高価格帯製品を選択せずに済む方法はあるのか」といった内容が挙げられる。Etronは、答えの一つが「低減ピンカウント(RPC:Reduced Pin Count)DRAM」だと考えているようだ。

これまで次世代メモリに関しては、さまざまな議論がなされてきた。例えば、「IoT(モノのインターネット)の登場によって生み出されたビジネスチャンスにどう対応するのか」「SRAMのような高価格帯製品を選択せずに済む方法はあるのか」といった内容が挙げられる。Etronは、答えの一つが「低減ピンカウント(RPC:Reduced Pin Count)DRAM」だと考えているようだ。

Etronのバイスプレジデントであり、イメージング/メモリ製品開発部門担当チーフサイエンティストを兼任するRichard Crisp氏は、「当社のDRAMは、JEDECロードマップに沿った既存のアーキテクチャとは異なり、高密度化や高速な転送速度、DDR4の帯域幅といった要件は全て不要な、さまざまなアプリケーションに対応することが可能だ。アプリケーションの中には、メモリ使用量が1Gビット未満とかなり少ないものが数多く存在するため、使い勝手に優れた適切なサイズのメモリだけを使用するということについて関心が高まっている」と述べている。

同氏は、「当社はこうした状況を受け、アプリケーションのニーズに対応すべく、一般的なDDRメモリのピン数を削減しながら、必要最低限のDRAMを提供する方法を模索してきた。当社が、実装面積が小さくピン数の少ないメモリを開発している間に、世界ではAI(人工知能)への関心が高まってきた。当初は、AIのことはあまり考えずに開発に着手したが、このような状況から、非常に興味深いソリューションを考え出すことができた」と述べる。

一般的なAIシナリオでは、エンドポイントでデータを収集してクラウドに送信し、両方のエンドポイントを相互接続する大規模なネットワークレイヤーで処理を行う。一方でCrisp氏は、「Etronは、“エンドポイント”と“エッジ”を区別したいと考えた。エンドポイントが、外界からデータを収集するセンサーとして、そしてエッジがローカルの集中型コンピュータとして機能することにより、複数センサーのデータの統合を一部実行して、高性能なメディアプロセッサと共通のストリームにすることができる。このエッジコンピュータは、ストリーム上で独自の分析を行ってから、一部の情報をクラウドに送信するため、エンドポイントよりも高い性能を必要とする。ただし、一部でサイズに関する制限がある」と述べている。

同氏は、「そこでEtronは、RPC DRAMでAIエッジアプリケーションをサポートするという答えを出した。AIエッジアプリケーションには、データを迅速に処理できるよう、参照画像などの相当量のデータストレージや、十分な高帯域幅が必要なためだ」と述べる。

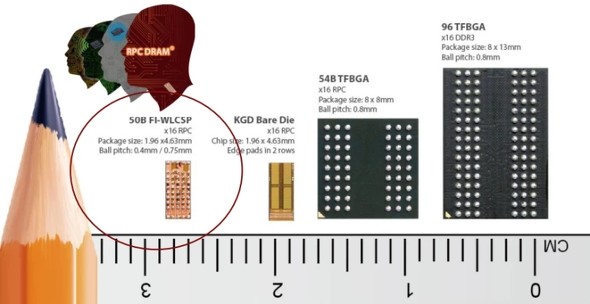

EtronのRPC(低減ピンカウント) DRAMは、超小型のFI-WLCSP(Fan In Wafer-Level Chip-Scale Package)にも搭載できるほど小さい 画像:Etron(クリックで拡大)

EtronのRPC(低減ピンカウント) DRAMは、超小型のFI-WLCSP(Fan In Wafer-Level Chip-Scale Package)にも搭載できるほど小さい 画像:Etron(クリックで拡大)Etronの製品に可能性を見いだしたのはLattice Semiconductor(以下、Lattice)である。同社の戦略担当マーケティングディレクターであるKambiz Khalilian氏は、同社がRPC DRAMを採用した理由として、その非常に小さなフォームファクタを挙げた。

同氏は「一般的に、RPC DRAMは標準的なDRAMと同等の性能をもたらすが、ピン数は少なくなる」と述べた。これは、Latticeがサポートする多くの“ディープエッジ”なアプリケーションにとって理想的なのだという。そうしたアプリケーションでは、性能とのトレードオフが重要になってくるからだ。RPC DRAMによって、全てのデータをクラウドに送信するには帯域幅が足りないところでも、低消費電力でデータを処理できるようになる。

Khalilian氏は、いくつかのアプリケーションでは、LatticeのFPGAに搭載されているよりも多くのメモリが必要になるとし、「RPC DRAMはそうしたシナリオで役立つ」と述べた。例えば、多くのエッジカメラアプリケーションでは、わずか数平方ミリメートルの実装面積の違いが重要になってくる。

Objective Analysisの主席アナリストであるJim Handy氏は、顧客が同技術に利点を見いだし、製品に取り込んだという事実は、Etronが提唱するコンセプトが潜在性を備えていることの証であると述べた。EtronのRPC DRAMではピン数が少ないシリアルインタフェースが採用されているが、それは業界が向かっている方向でもある。

EtronのRPC DRAMでは、「エッジで、より多くのデータを処理する」という新たに出現したユースケースに対応するため、比較的低密度な既存のDRAMが用いられている。それにより、デバイスとサーバ間で要求される帯域幅を最小限に抑えることができるとHandy氏は説明した。

関連記事

キオクシア、512ギガビットTLC製品を開発

キオクシア、512ギガビットTLC製品を開発

キオクシアは、3次元フラッシュメモリ「BiCS FLASH」の5世代目となる、112層積層プロセスを用いた製品を試作し、基本動作を確認した。試作したのは512ギガビットTLC製品で、2020年第1四半期(1〜3月)よりサンプル出荷を始める。 「成毛氏の路線引き継ぐ」キオクシア新社長、早坂氏

「成毛氏の路線引き継ぐ」キオクシア新社長、早坂氏

2020年1月29日、病気療養中の成毛康雄氏に代わってキオクシアHDおよび、子会社キオクシアの社長に、副社長だった早坂伸夫氏が就任した。同社は同日、東京都内で報道関係者向け説明会を実施。早坂氏は今後の方針について、「(成毛氏とは)お互いに戦略や考え方をきっちり共有できていた。基本的に今まで話し合ってきた路線でまずスタートしていく」と述べた。 サイプレス、ASIL-B準拠のNOR型フラッシュ

サイプレス、ASIL-B準拠のNOR型フラッシュ

サイプレス セミコンダクタは、「オートモーティブ ワールド2020」で、NOR型フラッシュメモリ「Semper NOR Flash」を搭載したフェールセーフクラスターや、大画面対応でハプティクス(触覚)機能などを新たに追加した、最新のタッチスクリーンコントローラIC「TrueTouch」などを紹介した。 AI技術の進化で注目が高まるReRAM

AI技術の進化で注目が高まるReRAM

次世代不揮発メモリの一つである抵抗変化メモリ(ReRAM)は、その大部分がまだ研究開発の段階にあるが、AI(人工知能)技術の進化で、注目が高まっている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- Rapidus、IIM-1を「世界初の前/後工程一貫工場に」

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- 三菱電機、福岡にパワー半導体新工場 設計〜生産一貫体制を構築

- 三菱電機、ローム・東芝との統合は「非常にポジティブ」

- 経産省がソニー画像センサー新工場に最大600億円補助

- 560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

- データセンター用CPUでも勢力伸ばすRISC-V

- AMD「ROCm」はNVIDIA「CUDA」に対抗できるのか

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)