5nm FinFET CMOS技術でクロック回路を開発:自動合成でSoC設計の期間を短縮

東京工業大学とソシオネクストの研究グループは、5nmのFinFET CMOSプロセス技術を用いた、高性能の分数分周型(フラクショナルN型)クロック回路を開発した。

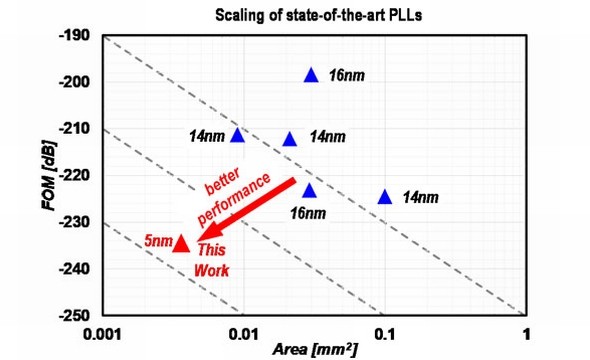

回路面積は0.0036mm2、FoMは−235dB

東京工業大学工学院電気電子系の岡田健一教授らとソシオネクストの研究グループは2020年2月、5nmのFinFET CMOSプロセス技術を用いた、高性能の分数分周型(フラクショナルN型)クロック回路を開発したと発表した。PLL回路全体をデジタル回路で構成でき、自動合成が可能なことからLSI設計ツールを用いてSoCの設計期間を短縮できるという。

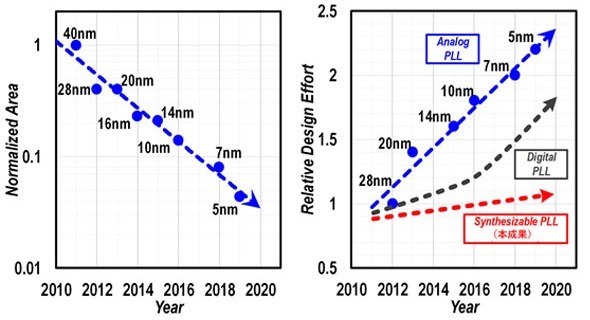

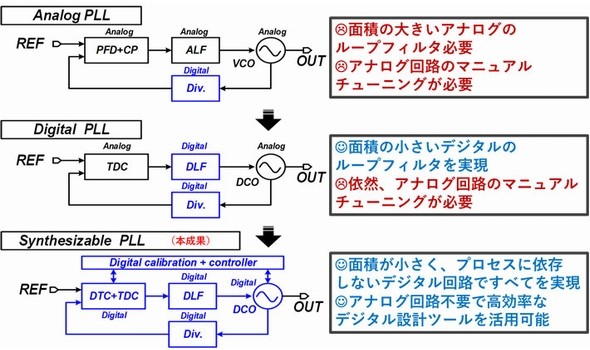

LSIに搭載されるクロック回路は、チップの動作に必要なクロック信号や通信用の搬送波信号を生成している。ここで用いられるクロック回路は、優れたジッタ特性を持つアナログ型のPLL方式が一般的である。しかし、デジタル回路に比べると回路面積が大きくなって性能が劣化したり、プロセスの微細化によって設計が難しくなったりしていた。

既に、デジタル型PLLの開発も行われているが、これまではデジタル制御発振器(DCO)と時間差デジタル変換器(TDC)の一部にアナログ回路が存在し、依然として手作業による設計が必要となっていた。

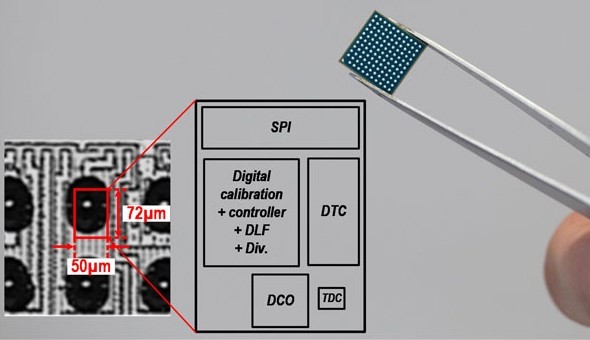

研究グループは今回、構成する回路ブロックを全てデジタル回路構成にした。これによってデジタル回路のように自動設計が可能となった。具体的には、タイミングをデジタル的に制御するデジタル時間変換器(DTC)とTDC回路を組み合わせた。この結果、TDC回路に必要な時間差範囲を狭めることができ、デジタル化に成功した。DCO回路でもデジタル補正技術を適用し、回路のデジタル化を可能にしたという。

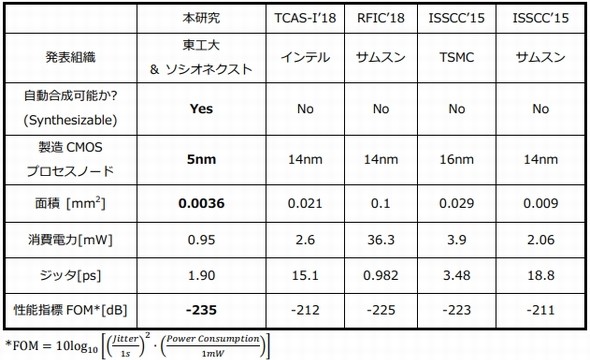

開発した技術を用い、任意の周波数を発生できる分数分周型PLLを作製した。高周波信号の生成が可能なリングオシレーター型発振器を採用するなどして小型化した。回路面積は0.0036mm2と極めて小さい。消費電力とジッタ特性に関する性能指標(FoM:Figure of Merit)も−235dBを達成している。消費電力は0.95mWで、スプリアスレベルは−44dBcと低い。スペクトル拡散クロック機能も備え、低電磁妨害特性を実現した。

関連記事

全固体リチウム電池応用の多値メモリ素子を開発

全固体リチウム電池応用の多値メモリ素子を開発

東京工業大学は、全固体リチウム電池を応用し、3値記録可能なメモリ素子を東京大学と共同で開発した。 ペロブスカイト太陽電池、放置して発電効率向上

ペロブスカイト太陽電池、放置して発電効率向上

東京工業大学物質理工学院応用化学系の脇慶子准教授らは2019年10月、ペロブスカイト太陽電池を作製した時に、初期特性が安定しなくても常温常圧のまま放置するだけで、発電効率が向上する技術を開発した。 東工大、放射光でセラミックス内部の欠陥を観察

東工大、放射光でセラミックス内部の欠陥を観察

東京工業大学は、大型放射光施設「SPring-8」の放射光マルチスケールX線CTを用いて、セラミックス内部の欠陥を観察することに成功した。 IGZOの性能を左右する微量水素の振る舞いを解明

IGZOの性能を左右する微量水素の振る舞いを解明

高エネルギー加速器研究機構(KEK)と東京工業大学らの研究グループは、あたかも水素のように振る舞う素粒子「ミュオン」を用い、微量の不純物水素が酸化物半導体「IGZO」の導電性に影響を与えるメカニズムの一端を解明した。 酸窒化物単結晶を用い、強誘電性を初めて実証

酸窒化物単結晶を用い、強誘電性を初めて実証

北海道大学と東京工業大学の研究グループは、酸窒化物ペロブスカイトBaTaO2N単結晶が強誘電体であることを実証した。 MEMS加速度センサー、高感度で低ノイズを実現

MEMS加速度センサー、高感度で低ノイズを実現

東京工業大学とNTTアドバンステクノロジの研究グループは、複数の金属層を積層した構造とすることにより、従来に比べ感度を100倍以上に高め、ノイズは10分の1以下に抑えたMEMS加速度センサーを開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- AIと地政学リスクが招く深刻なメモリ危機

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 26年の半導体市場は64%成長で1.3兆ドルに NAND価格は234%上昇

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

左は半導体プロセスのスケーリング、右はPLL回路設計の難易度 出典:東京工業大学、ソシオネクスト

左は半導体プロセスのスケーリング、右はPLL回路設計の難易度 出典:東京工業大学、ソシオネクスト PLLの回路ブロック図。下図が今回開発したシンセサイザブルPLL 出典:東京工業大学、ソシオネクスト

PLLの回路ブロック図。下図が今回開発したシンセサイザブルPLL 出典:東京工業大学、ソシオネクスト 開発した分数分周型クロック回路を搭載したチップ写真 出典:東京工業大学、ソシオネクスト

開発した分数分周型クロック回路を搭載したチップ写真 出典:東京工業大学、ソシオネクスト 20nmノード以降の先端CMOSプロセスにおけるPLL性能比較 出典:東京工業大学、ソシオネクスト

20nmノード以降の先端CMOSプロセスにおけるPLL性能比較 出典:東京工業大学、ソシオネクスト 20nmノード以降の先端CMOSプロセスにおけるPLL回路面積および、FoM比較 出典:東京工業大学、ソシオネクスト

20nmノード以降の先端CMOSプロセスにおけるPLL回路面積および、FoM比較 出典:東京工業大学、ソシオネクスト