静電気放電から電子回路を守るESDサプレッサ:福田昭のデバイス通信(234) 2019年度版実装技術ロードマップ(44)(1/2 ページ)

今回は、ESD対策に特化した電子部品「ESDサプレッサ」の概要を解説する。バリスタとの違いや、主な仕様を取り上げる。

静電気放電(ESD)対策に特化した電子部品

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」に関する完成報告会(2019年6月4日に東京で開催)と同ロードマップの概要をシリーズでご報告している。今回はその第44回である。

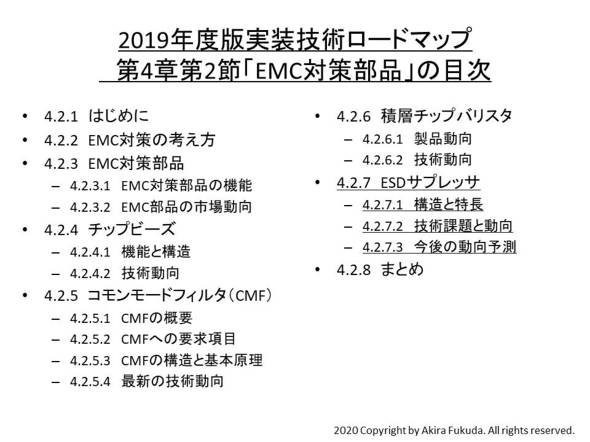

本シリーズの第31回から、第4章「電子部品」の概要を説明してきた。第4章「電子部品」は、「4.1 LCR部品」「4.2 EMC対策部品」「4.3 センサ」「4.4 コネクタ」「4.5 入出力デバイス」の5つの節に分かれる。第39回からは、「4.2 EMC対策部品」の概要を紹介している。第40回は雑音対策部品の代表である「チップビーズ(チップフェライトビーズ、チップ型フェライトビーズインダクタ)」の概要を、第41回と第42回は同じく雑音対策部品の代表である「コモンモードフィルタ(コモンモードチョークコイル)」の概要をご説明した。

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第31回から、第4章「電子部品」(プログラムの8番)の概要を紹介している。出典:JEITA(クリックで拡大)

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第31回から、第4章「電子部品」(プログラムの8番)の概要を紹介している。出典:JEITA(クリックで拡大)前回(第43回)からはEMC対策部品の中でも、電子回路を雷サージや静電気放電(ESD)などの雑音から保護する部品を紹介している。前回は「積層チップバリスタ」および「バリスタ」の概要を説明した。今回はESD対策に特化した電子部品「ESDサプレッサ」の概要を解説する。

バリスタとESDサプレッサの違い

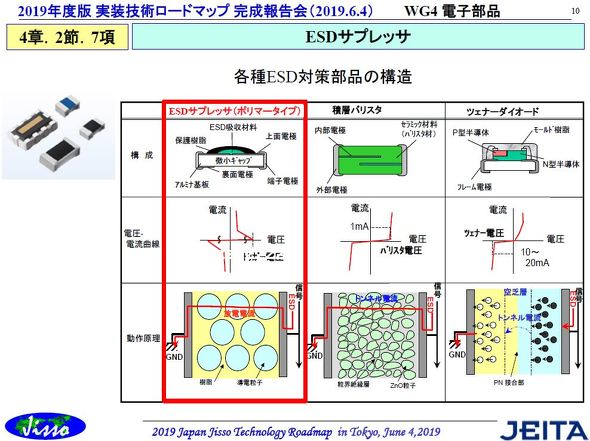

「ESDサプレッサ」は「バリスタ」と同様に2端子部品であり、通常は非常に高い抵抗値を有する絶縁素子である。電源線(あるいは信号線)と接地線(グランド)の間にESDサプレッサを挿入して使う。通常は、ESDサプレッサはバリスタと同様にコンデンサに見える。ESDに伴う高電圧電流パルスが加わると、ESDサプレッサが通電することで印加電圧を下げ、電子回路を保護する。

ESDサプレッサがバリスタと大きく違うのは、静電容量と電流電圧特性、応答速度だ。ESDサプレッサの静電容量は0.1pF以下と極めて小さい。バリスタの小容量品と比べても10分の1である。このため、高速の信号ラインに適する。

また電流電圧特性は独特である。印加電圧をゼロから上げていくと、一定の電圧まではほぼ絶縁素子のように振る舞う。ある電圧を超えると急激に電流が流れ出すとともに、電圧が低下する。それからほぼ一定の電圧を維持しながら、電流が急激に増えていく。電流が流れ始める電圧はかなり高く、数百Vに達する。その代わりにESDサプレッサの応答速度は極めて高い。5ナノ秒以内で応答し、電圧が下がり始める。応答時間はバリスタの1000分の1と短い。

ESDサプレッサは内部に微小なギャップを有しており、ESDの高電圧電流パルスが印加されるとこのギャップ間で放電が発生することによって電流が流れ、電圧パルスの高さを急速に減衰させる。部品の外形は通常、表面実装型の角型チップ部品である。1608(長さ1.6mm×幅0.8mm)サイズや1005(1.0mm×0.5mm)サイズ、0603(長さ0.6mm×幅0.3mm)サイズなどが市販されている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増