東京工大ら、Ka帯衛星通信向け無線ICを開発:シリコンCMOSプロセスで実現

東京工業大学とソシオネクストは、標準シリコンCMOSプロセスを用い、Ka帯衛星通信向け無線ICを開発した。従来は6〜9個のICを用いていた通信機能を1チップで実現している。

受信機2系統を内蔵、二偏波MIMOと周波数多重を選択可能

東京工業大学工学院電気電子系の岡田健一教授や白根篤史助教らによる研究グループと、ソシオネクストの研究グループは2020年8月、標準シリコンCMOSプロセスを用い、Ka帯衛星通信向け無線ICを開発したと発表した。

開発した無線ICは、インダクターの相互結合を利用した低雑音増幅器(LNA)と干渉波を打ち消す回路を採用することで、低雑音かつ高線形性で干渉波に強いトランシーバーを実現している。しかも、ダイレクトコンバージョン方式を用いることで、従来のスーパーヘテロダイン方式に比べ部品点数を削減することが可能である。

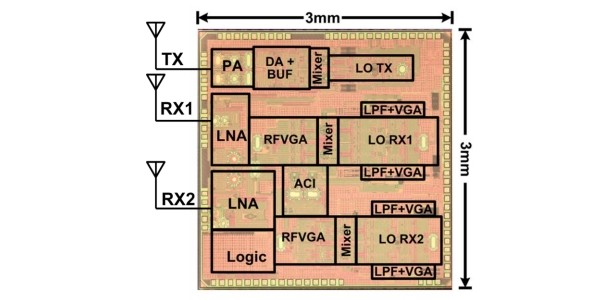

無線ICは、65nmのシリコンCMOSプロセスを用いて試作した。3×3mmのチップサイズに送信機1系統と受信機2系統を集積している。従来は6〜9個のICを用いていた通信機能を1チップで実現した。

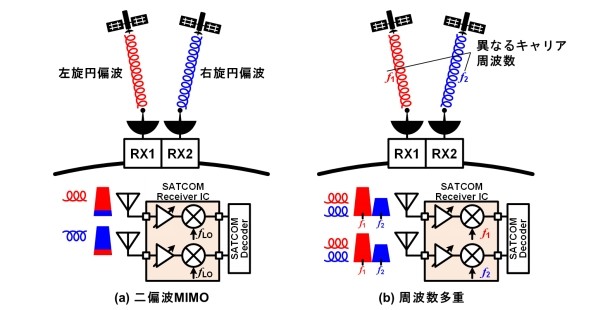

内蔵した受信機は、内部のスイッチを切り替えることで「二偏波MIMOモード」と「周波数多重モード」のいずれかを選択できる。二偏波MIMOモードでは、右旋円偏波と左旋円偏波の2種類を利用すると、最大2倍の通信容量を実現できる。周波数多重モードでは、キャリア周波数が異なる2つの変調信号を同時に受信することができ、通信帯域幅を拡大して通信容量を増やすことができるという。

研究グループは、試作した無線ICの通信特性を評価した。この結果、送信機は27〜31GHzで動作し、飽和出力電力は19dBmであった。シンボルレート150Mbaudの場合に256APSK変調を用い、データレート1.2Gビット/秒を達成。一方、受信機は17〜21GHzの周波数範囲で動作し、雑音指数は5.0dB、線形性IIP3(3次入力インターセプトポイント)は0.2dBmを達成した。

関連記事

東工大ら、「p型透明超伝導体」を初めて実現

東工大ら、「p型透明超伝導体」を初めて実現

東京工業大学と東北大学は共同で、低温では超伝導体となる「層状ニオブ酸リチウム(LiNbO2)」が、常温で「p型透明導電体」になることを発見した。 有機トランジスタ用結晶膜成膜の高速化に成功

有機トランジスタ用結晶膜成膜の高速化に成功

東京工業大学は、有機トランジスタ用半導体の超高速塗布成膜に成功した。ディップコート法と液晶性有機半導体を活用することで、従来の溶液プロセスに比べ成膜速度は2000倍以上も速い。 岡山大ら、強誘電体の傾斜したバンド構造を初観測

岡山大ら、強誘電体の傾斜したバンド構造を初観測

岡山大学と高輝度光科学研究センター(JASRI)、産業技術総合研究所(産総研)、東京工業大学、パリサクレー大学の共同研究グループは、電気分極に由来する強誘電体の傾斜したバンド構造の観測に初めて成功した。 東京工大、極薄ウエハーのレーザー加工技術を開発

東京工大、極薄ウエハーのレーザー加工技術を開発

東京工業大学は、極薄ウエハーにダメージを与えずに、ダイシングストリート幅を従来の4分の1に縮小できるレーザーダイシング加工技術を開発した。 偏波MIMO対応ミリ波フェーズドアレイ無線機開発

偏波MIMO対応ミリ波フェーズドアレイ無線機開発

東京工業大学とNECの研究グループは、5G(第5世代移動通信)システムの通信速度をさらに高速化できる「偏波MIMO対応のミリ波フェーズドアレイ無線機」を共同で開発した。同じ周波数帯域幅を用いた従来方式に比べ、通信速度を2倍にすることが可能となる。 5nm FinFET CMOS技術でクロック回路を開発

5nm FinFET CMOS技術でクロック回路を開発

東京工業大学とソシオネクストの研究グループは、5nmのFinFET CMOSプロセス技術を用いた、高性能の分数分周型(フラクショナルN型)クロック回路を開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

受信機は、内蔵したスイッチで「二偏波MIMOモード」と「周波数多重モード」を選択できる 出典:東京工業大学、ソシオネクスト

受信機は、内蔵したスイッチで「二偏波MIMOモード」と「周波数多重モード」を選択できる 出典:東京工業大学、ソシオネクスト 65nmのCMOSプロセスを用いて試作した無線ICのチップ写真 出典:東京工業大学、ソシオネクスト

65nmのCMOSプロセスを用いて試作した無線ICのチップ写真 出典:東京工業大学、ソシオネクスト