多層配線の微細化と性能向上を両立させる要素技術:福田昭のデバイス通信(284) Intelが語るオンチップの多層配線技術(5)

今回から、多層配線の微細化と性能向上を両立させる要素技術について解説していく。

微細化による性能の低下をいくつかの要素技術で緩和する

半導体のデバイス技術と回路技術に関する国際学会「VLSIシンポジウム」では、「ショートコース(Short Course)」と呼ぶ技術講座を開催してきた。2020年6月に開催されたVLSIシンポジウムのショートコースは、3つの共通テーマによる1日がかりの技術講座が設けられていた。その中で「SC1:Future of Scaling for Logic and Memory(ロジックとメモリのスケーリングの将来)」を共通テーマとする講演、「On-Die Interconnect Challenges and Opportunities for Future Technology Nodes(将来の技術ノードに向けたオンダイ相互接続の課題と機会)」が非常に興味深かった。そこで講演の概要を本コラムの第280回からシリーズでお届けしている。講演者はIntelのMauro J. Kobrinsky氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前々回(第282回)では代表的な金属配線である「銅(Cu)配線」の寸法と電気抵抗(単位長当たりの抵抗値)の関係を、前回(第283回)では銅(Cu)配線の寸法と静電容量(単位長当たりの容量値)の関係をご説明した。今回からは、多層配線の微細化と性能向上を両立させる要素技術について解説していこう。

サブトラクティブな製造、2次元材料のキャップ、高アスペクト比の埋め込み

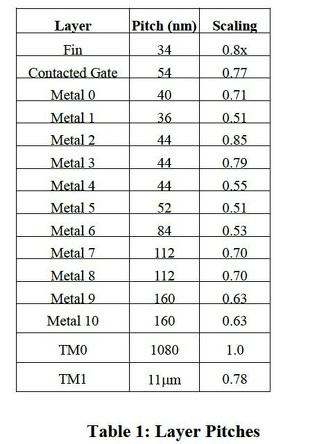

例としてIntelが開発した10nmノードの大規模高性能ロジック用多層配線を取り上げる。この多層配線は12層の金属配線によって形成される。最下層である第0層(M0層)のピッチは40nm、その上にある第1層(M1層)のピッチは36nmと極めて狭い。さらに上の第2層(M2層)〜第4層(M4層)は44nmピッチ、第5層(M5層)は52nmピッチ、第6層(M6層)は84nmピッチとなっている。第7層(M7層)以上の配線ピッチは100nm超とかなり広い。

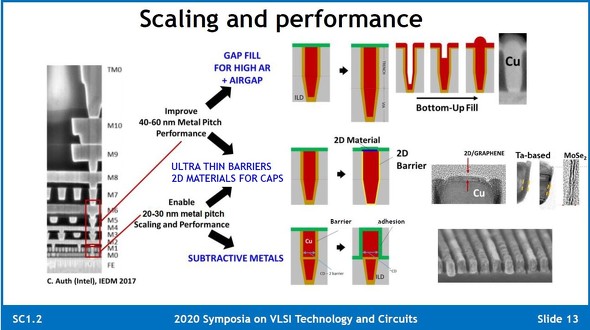

多層配線は今後、2つの方向で進化する。1つは最も微細な最下層付近の配線部(M0層〜M1層)である。こちらは今後もさらに微細化する。配線ピッチを20nm〜30nmと極めて狭くする。ピッチを狭くしつつ、性能を維持する。例えば現在のデュアルダマシン法による銅の配線ではなく、サブトラクティブ法による代替金属の配線が考えられる。極めて薄いバリア層、2次元材料のキャップ層といった要素技術も将来の有力候補である。

多層配線の性能を向上させる要素技術の例。左は10nmノードの大規模高性能ロジック用多層配線構造の断面を電子顕微鏡で観察した画像。中央は配線技術の方向性。右は要素技術の具体例。出典:Intel(クリックで拡大)

多層配線の性能を向上させる要素技術の例。左は10nmノードの大規模高性能ロジック用多層配線構造の断面を電子顕微鏡で観察した画像。中央は配線技術の方向性。右は要素技術の具体例。出典:Intel(クリックで拡大)もう1つは、最下層よりもピッチの長い配線部(M2層〜M6層付近)である。配線ピッチは40nm〜60nm前後とやや緩い。

この部分では微細化よりも、性能の向上に重点を置く。極めて薄いバリア層、2次元材料のキャップ層といった要素技術はこの部分でも将来の有力候補である。高いアスペクト比の溝に金属を埋め込む技術や絶縁膜にエアギャップを導入する技術などにも、期待がかかる。

これらの要素技術は、次回以降でもう少し詳しく説明していく。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

銅(Cu)配線の微細化と抵抗値の増大

銅(Cu)配線の微細化と抵抗値の増大

引き続き、オンチップの多層配線技術に関するIntelの講演内容を紹介する。今回は、銅配線の寸法と電気抵抗の関係を説明する。 ムーア則の維持に貢献する配線技術

ムーア則の維持に貢献する配線技術

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。 オンチップの相互接続技術を過去から将来まで概観

オンチップの相互接続技術を過去から将来まで概観

2020年6月にオンラインで開催された「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介する。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 HDD大手Seagateの四半期売上高は前年同期比で2桁の減少

HDD大手Seagateの四半期売上高は前年同期比で2桁の減少

今回は、米Seagate Technologyの2021会計年度第1四半期の業績を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増