3D NANDフラッシュの高層化と記憶密度の推移:福田昭のストレージ通信(186) アナリストが語る不揮発性メモリの最新動向(13)(2/2 ページ)

» 2021年03月23日 10時30分 公開

[福田昭,EE Times Japan]

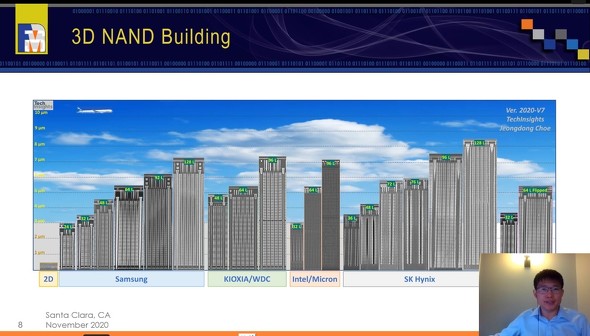

超高層ビルディングと化す3D NANDのメモリセルアレイ

3D NANDフラッシュの高層化はしばしば、高層ビルディングに例えられる。対するプレーナー(2D)NANDフラッシュはさしずめ、平屋あるいは低層のアパートメントだろうか。

2D NANDフラッシュの高さは、1μmに満たない。これに対して3D NANDフラッシュは24層〜32層で既に3μm前後と、大規模半導体集積回路(LSI)としては異常な高さに達していた。64層は5μm前後、72層は6μm前後とさらに高層化する。96層は7μm前後に達する。

高層化は、メモリセルを縦方向に接続する孔(「メモリスルーホール」と呼ぶ)の形成を著しく難しくする。このため、メモリスルーホールの形成を2段階で実施するプロセスが採用されている。例えば64層であれば、32層のスルーホールを2回形成する工程に分ける。

3D NANDフラッシュの高層ビルディング。配布資料では薄いアミをかけていた。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)

3D NANDフラッシュの高層ビルディング。配布資料では薄いアミをかけていた。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大) 3D NANDフラッシュの高層ビルディング。講演スライドではメモリセルアレイの断面を電子顕微鏡で観察した画像を示していた。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」のスライド(クリックで拡大)

3D NANDフラッシュの高層ビルディング。講演スライドではメモリセルアレイの断面を電子顕微鏡で観察した画像を示していた。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」のスライド(クリックで拡大)なおSamsungだけは、メモリスルーホールの形成を1回で済ませている。同じ積層数でも、Samsungの3D NANDはあまり高くない。特に92層と128層では、他社に比べて低い。メモリスルーホール作成の難しさを緩和していることがうかがえる。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR