「VLSI Circuitsシンポジウム」の注目論文:VLSIシンポジウム2021(2/2 ページ)

アナログとセンサー関連

Intelは、サーバ向けの高効率GaNパワーモジュールを発表する(同:C3-1)。データセンターでは、高効率で5Vから1Vに降圧するDC-DCコンバーターが求められている。Intelは5Vと低電圧のGaNパワートランジスタを開発。同トランジスタとCMOSドライバーICを、4×4mmのパッケージに集積したDC-DCコンバーターを発表する。スイッチング周波数は3MHz。5V入力/1V出力において、最大94.2%の変換効率を実現した。

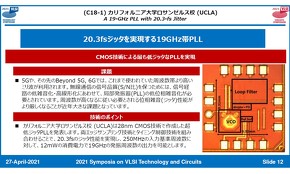

米カリフォルニア大学ロサンゼルス校(UCLA)は、CMOS技術で製造した超低ジッタPLL(Phase Locked Loop)を発表する(同:C18-1)。5G以降の通信では、無線通信の信号品質を保つために、PLLの低位相雑音化が求められている。UCLAは、両エッジサンプリング技術とタイミング制御技術を組み合わせて、20.3フェムト秒のジッタ性能を実現した。250MHzの入力基準周波数に対して、12mWの消費電力で19GHzという高い発振周波数の出力が可能になる。

韓国Samsung Electronicsは、Cu-to-Cuチップ接合技術によるA-Dコンバーター搭載型CMOSイメージセンサーを発表する(同:JFS4-4)。高画質化と高速化を両立するために、画素ごとにA-Dコンバーターを搭載する構成を採用。光検出用のチップと、A-Dコンバーターを搭載したチップを、Cu PAD経由で高密度かつ高精度に接続。これにより、2.6電子の低ノイズを実現し、最高で960フレーム/秒での動作が可能になるとする。

ドイツRobert Boschは、従来比4倍のワイドレンジでジャイロセンサーの計測を実現するアナログフロントエンド回路を提案する(同:C19-1)。回路方式の改善と最適化により、従来の回路と比較して約4倍となる±8000deg./秒という広い計測レンジを達成した。ノイズフロアは0.0047deg./秒/√Hzである。

米ミシガン大学は、脳センサー向けの超小型神経信号測定チップを発表する(同:C2-2)。光で駆動する脳測定デバイスは、光がパッケージの隙間からチップに届いてしまって誤作動するといった課題がある。ミシガン大学は、回路の構造と設計を工夫することで、光が当たっても安定して神経信号を計測、処理し、送信する回路を提案する。生体組織の限界である300μW/mm2の照射耐性を達成しており、これによって光による誤作動の問題をほぼ解消できるとする。消費電力は、38℃で0.57μW。

関連記事

TSMCの最新プロセスまとめ、3nm以降の開発も進行中

TSMCの最新プロセスまとめ、3nm以降の開発も進行中

TSMCは2021年6月1〜2日に、自社イベント「2021 Technology Symposium」をオンラインで開催した。同イベントで発表された最新プロセスノードなどをまとめる。 電源/接地線の埋め込みで回路ブロックの電圧降下を半分以下に低減

電源/接地線の埋め込みで回路ブロックの電圧降下を半分以下に低減

電源/接地配線を基板側に埋め込む「BPR(Buried Power Rails)」について解説する。 176層3D NAND搭載SSDや1αnm LPDDR4Xの量産を開始

176層3D NAND搭載SSDや1αnm LPDDR4Xの量産を開始

Micron Technology(以下、Micron)は2021年6月2日(台湾時間)、オンラインで開催中の「COMPUTEX TAIPEI 2021」(2021年5月31日〜6月30日)で、176層の3D(3次元) NAND型フラッシュメモリを採用したPCIe Gen4対応SSDの量産出荷を発表した。 東京大ら、3次元集積可能なメモリデバイスを開発

東京大ら、3次元集積可能なメモリデバイスを開発

東京大学は、神戸製鋼所およびコベルコ科研と共同で、Snを添加したIGZO材料(IGZTO)を用いた3次元集積メモリデバイスを開発、動作実証に成功した。プロセッサの配線層上に大容量メモリを混載することが可能となる。 複数AIアクセラレーター搭載の評価チップを試作

複数AIアクセラレーター搭載の評価チップを試作

新エネルギー・産業技術総合開発機構(NEDO)と産業技術総合研究所(産総研)および、東京大学は共同で、仕様が異なる6種類のAIアクセラレーターを搭載した評価チップ「AI-One」を設計、試作を始めた。これを活用すると、短い期間で安価にAIチップの設計と評価が可能になる。 東芝、トリプルゲートIGBTとゲート制御技術を開発

東芝、トリプルゲートIGBTとゲート制御技術を開発

東芝は、スイッチング損失を全体で最大40.5%も低減できる「トリプルゲートIGBT」を開発した。再生可能エネルギーシステムや電気自動車(EV)などに搭載される電力変換器の高効率化に向けて、早期実用化を目指す。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増