コンプリメンタリFET(CFET)でCMOS基本セルの高さを半分に減らす:福田昭のデバイス通信(309) imecが語る3nm以降のCMOS技術(12)(1/2 ページ)

引き続き、FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET/CFET)の講演部分を紹介する。今回は、CFETがCMOS基本セルの微細化に与えるメリットを具体的に解説する。

選択の余地がなくなるCMOS基本セルの低背化手法

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前回から「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している(クリックで拡大)

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前回から「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している(クリックで拡大)前回から、3番目のパートである「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している。前回は、「コンプリメンタリFET(C(Complementary)FET)」の基本的な概念と期待できる利点を説明した。今回はCFETがCMOS基本セル(スタンダードセル)の微細化に与えるメリットを具体的に解説する。

CMOSロジックの基本セルを縮小する重要な手法が、セルの高さ(CH:Cell Hight)を下げる「低背化」であることは本シリーズで既に述べた。CMOS基本セル(インバーター)のレイアウトでは複数のチャンネルが水平方向に走る。チャンネルと平行にレイアウトする最下層金属配線の本数(トラック数:T)が、セルの高さ(CH)を決める。金属配線の本数(トラック数)を減らすことが、セル高さの低減に直結する。

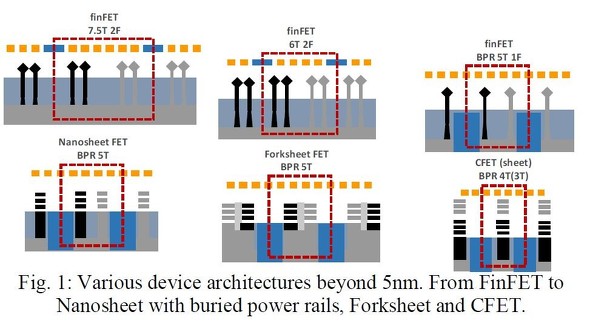

当初、トラック数(T)の削減は、トランジスタ技術をFinFETとするCMOS基本セルで実施された。7.5T(7.5トラック)と6TはFinFETのままで、トラック数を減らすことができた。しかし5T(5トラック)になると、従来技術の延長ではセル高さの低減が難しくなる。まず考えられたのが、FinFETのまま、金属配線の電源/接地線を基板側に埋め込む「BPR(Buried Power Rail)」である。これで実効的には金属配線(トラック)を2本近く減らせる。

5nm世代以降のトランジスタ技術(断面構造図)のオプション。上の3つはFinFET、下は左からナノシートFET、フォークシートFET、CFETである。出典:imecが2019年12月に国際学会IEDMで発表した論文「Enabling Sub-5nm CMOS Technology Scaling Thinner and Taller!」(論文番号29.4)から(クリックで拡大)

5nm世代以降のトランジスタ技術(断面構造図)のオプション。上の3つはFinFET、下は左からナノシートFET、フォークシートFET、CFETである。出典:imecが2019年12月に国際学会IEDMで発表した論文「Enabling Sub-5nm CMOS Technology Scaling Thinner and Taller!」(論文番号29.4)から(クリックで拡大)BPRとFinFETの組み合わせでは、5T(5トラック)を実現するフィンの枚数がトランジスタ当たりで1枚となり、トランジスタの性能が低下する恐れがある。そこで、トランジスタをFinFETからナノシート構造やフォークシート構造などに変更することで、FinFETに比べてトランジスタの性能を向上するとともに、トランジスタの密度を高めやすくする。高さが5T(5トラック)のCMOS基本セルにはFinFET、ナノシート、フォークシートの3つのオプションが混在することになる。

ただし4T(4トラック)以降の低背化は、pチャンネルFETとnチャンネルFETをシリコン表面に並べたCMOSデバイス構造では、難しい。pチャンネルFETとnチャンネルFETをシリコン表面と垂直に積層するCFET(コンプリメンタリFET)を導入することが求められる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- 次世代パワー半導体 「期待の5材料」の現在地