EE Times Japan >

LSI >

コンプリメンタリFET(CFET)でCMOS基本セルの高さを半分に減らす:福田昭のデバイス通信(309) imecが語る3nm以降のCMOS技術(12)(2/2 ページ)

» 2021年07月13日 11時30分 公開

[福田昭,EE Times Japan]

基本セルの低背化と入出力ピン密度の向上がメリット

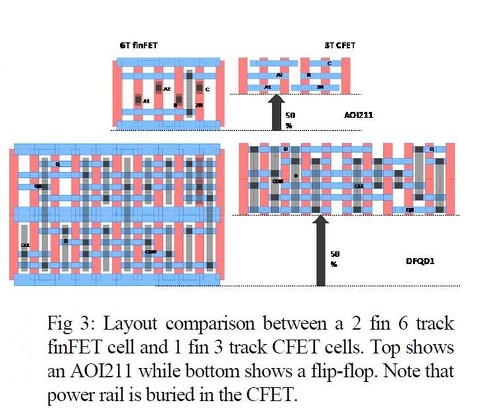

CFETの導入によって、CMOS基本セルの高さを4T(トラック)および3Tに低くできるとimecは考える。例えば6T(6トラック)の2フィンタイプFinFETと同じ機能の論理セル(AOI(AND-OR-INVERT)211セルとDFQD1セル(フリップフロップ))を、CFETでは半分の高さである3T(3トラック)でレイアウト可能になる。

FinFETによる論理回路セル(6トラック)とCFETによる論理回路セル(3トラック)。CFETによって論理回路セルの高さをFinFETの50%にできる。出典:imecが2018年6月に国際学会VLSI技術シンポジウムで発表した論文「The Complementary FET(CFET) for CMOS scaling beyond N3」(論文番号T13-3)から(クリックで拡大)

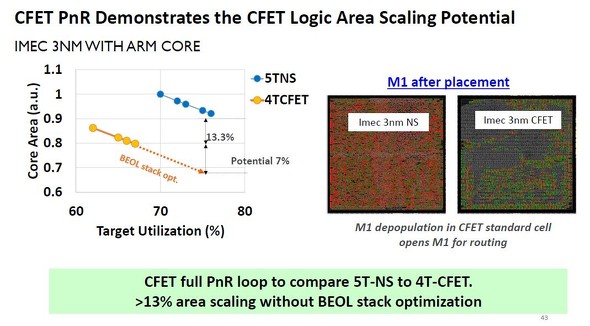

FinFETによる論理回路セル(6トラック)とCFETによる論理回路セル(3トラック)。CFETによって論理回路セルの高さをFinFETの50%にできる。出典:imecが2018年6月に国際学会VLSI技術シンポジウムで発表した論文「The Complementary FET(CFET) for CMOS scaling beyond N3」(論文番号T13-3)から(クリックで拡大)また3nm世代のArmプロセッサコアを想定すると、5Tのナノシート構造に比べて4TのCFETはコアの面積が13.3%減少する。さらに、CFETでは最下層金属配線(M0)を全て相互接続(ルーティング)に使えるので、M0と直交する第1層金属配線(M1)を入出力ピンや相互接続などに割り当てられる。この利点を生かして金属配線工程(BEOL)を最適化すると、コアの面積をさらに7%減少できると見積もる。

Armプロセッサコアのシリコン面積の比較(相対値)。5Tのナノシート構造に比べて4TのCFETはコアの面積が13.3%減少する(左)。またCFETは第1層金属配線(M1)のルーティングに余裕ができる(右)ので、金属配線工程(BEOL)の最適化によってコア面積をさらに減らせる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)(クリックで拡大)

Armプロセッサコアのシリコン面積の比較(相対値)。5Tのナノシート構造に比べて4TのCFETはコアの面積が13.3%減少する(左)。またCFETは第1層金属配線(M1)のルーティングに余裕ができる(右)ので、金属配線工程(BEOL)の最適化によってコア面積をさらに減らせる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)(クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

FinFETの「次の次」に来るトランジスタ技術

FinFETの「次の次」に来るトランジスタ技術

今回から、「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を解説する。 東京大学ら、FeAs-InAs単結晶超格子構造を作製

東京大学ら、FeAs-InAs単結晶超格子構造を作製

東京大学らの研究グループは、InAs半導体結晶中のほぼ1原子層の平面にFe原子を配列した「FeAs-InAs単結晶超格子構造」を作製することに成功し、さまざまな新しい物性を観測したと発表した。 2021年半導体市場規模は5272億米ドル、WSTS春季予測

2021年半導体市場規模は5272億米ドル、WSTS春季予測

WSTS(世界半導体統計)は2021年6月8日、2021年春季半導体市場予測を発表した。それによると2021年世界半導体市場規模は2020年比19.7%増の5272億2300万米ドルと大きく拡大し、初めて5000億米ドルの大台を突破するとした。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

Special SitePR

あなたにおすすめの記事PR