SNNを加速するニューロモーフィックAIチップを開発:オランダの新興企業(2/2 ページ)

超低消費電力のプログラマブルチップ

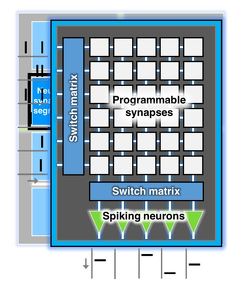

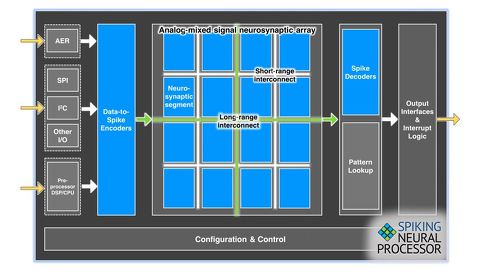

Innateraのスパイキングニューラルプロセッサは、スパイキングニューロンとシナプスの並列アレイを利用することにより、精密な時間ダイナミクスで連続時間SNNを加速させる。このデバイスは、データの処理方法に関する時間の概念を取り込むことが可能なSNNの能力を利用するために開発された、アナログ/ミックスドシグナルアクセラレーターである。

Innateraのコンピューティングファブリックの重要な側面の1つとして、プログラマビリティが挙げられる。プログラマビリティが重要視される理由は、2つある。

1つ目は、異なる種類のSNNをチップ上でプログラミングできるという点だ。ニューロンは、柔軟な方法で接続する必要がある。脳は、非常に複雑なニュラルネットワークトポロジを使用して、物事を効率的に進める。そのためには、ニューロン間を複雑に接続して、それをシリコンで再現しなければならない。

2つ目は、性能の最適化である。SNNでは、情報をビットとして表示するのではなく、正確なタイミングのスパイクとして表示する。スパイクのタイミングを非常に微細なレベルで操作することにより、データに関する洞察を引き出さなければならない。このため、ニューロンと、ニューロン間の接続(シナプス)は、複雑なタイミング行動を示すことになる。これらの行動を、InnateraのSDK(ソフトウェア開発キット)で調整することにより、性能を最適化することができる。

“デジタルアシスト”なアナログチップ

Innateraは、「当社のチップは、アナログミックスドシグナルまたは”デジタルアシストアナログ”である」と説明する。ニューロンとシナプスをアナログシリコンに実装することにより、超低消費電力を維持することができる。またアナログエレクトロニクスは、持続的なタイムネットワークを実現することが可能だ(デジタルエレクトロニクスの場合は、離散化が必要)。これは、SNNにとって非常に重要である。というのも、SNNには本質的に時間の概念があり、一定期間にわたって特定のステータスを保持できるようにする必要があるためだ。

Kumar氏は、「アナログ領域では、これを非常に簡単に実行することができる。ステータスを維持しなければならないという複雑性を、ネットワークトポロジーに移行する必要がないからだ。われわれがアナログ領域で実行するのは、そのようなステータス情報がもともと計算エレメントに保持されているためだ」と述べる。

チップ上の計算エレメント間や異なる種類のチップ間などにおいて、製造上の小さな不一致が生じると、アナログ領域でニューラルネットワークを正確に実行する上で問題が生じる可能性がある。Innateraのソリューションは、ニューロンをセグメントにグループ化するというもので、パス長やニューロンの数に適合するよう注意深く設計されている。

Kumar氏は、「セグメントは基本的に、アナログ回路の中に一般的に存在する非理想性を最小化しながら、その優れた点を最大限に活用できるよう設計されている。これは全て基本的に、セグメント内のニューロンが確実に決定的動作を示し、周囲のニューロンと同じ方法で機能できるようにするためだ」と述べている。

異なる種類のチップ間に不一致があると、同じトレーニングを受けたネットワークが実地でデバイスに展開された場合に、問題が発生する可能性がある。Innateraは、この問題をソフトウェアで回避している。

Innateraが今回発表したチップのサンプル出荷は、2021年内にも開始される予定だ。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

Neuromorphicがブレイクする予感 ―― メモリ国際学会と論文検索から見える動向

Neuromorphicがブレイクする予感 ―― メモリ国際学会と論文検索から見える動向

2018年、2019年のメモリの学会「International Memory Workshop」(IMW)に参加し、見えてきた新メモリの動向を紹介したい。 脳型コンピュータはAIチップと競合するのか?

脳型コンピュータはAIチップと競合するのか?

新しいニューロモーフィックチップは、同様に最先端の分野であるAI(人工知能)アクセラレーターは、“競合”となるのか。ニューロモーフィックチップやAIアクセラレーターを開発する企業のCEOに、見解を聞いた。 Intel、1億ニューロンを組み込んだ脳型システムを発表

Intel、1億ニューロンを組み込んだ脳型システムを発表

Intelは2020年3月18日(米国時間)、約1億ニューロンの演算能力を備えた新しいニューロモーフィックコンピューティングシステム「Pohoiki(“ポホイキ”のように発音) Springs」を発表した。 Baidu、ニューロモーフィックICを手掛ける企業に投資

Baidu、ニューロモーフィックICを手掛ける企業に投資

スイスのスタートアップ企業であるaiCTX(エーアイコルテクスのように発音)は、Baidu Venturesからの150万米ドルのPre Aラウンドを完了した。 エッジAIを安価・高速に、FPGAを駆使するベンチャー

エッジAIを安価・高速に、FPGAを駆使するベンチャー

LeapMindは2018年8月31日、東京都内で同社初となるプライベートカンファレンス「DeLTA TECH 2018」を開催した。このイベントでは、LeapMindの強みとなる技術が多く明かされていた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

InnateraのSumeet Kumar氏

InnateraのSumeet Kumar氏